明古微半导体

MGME SEMICONDUCTOR

碳化硅功率器件+电驱方案

新能源汽车.充电桩.工业电源.光伏储能.电力电子.低空飞行器...

国产碳化硅 就找明古微

技术学院

STUDY

1–35kV范围内中压(MV)配电和转换中的一些电力电子应用包括用于太阳能等可再生能源系统的并网逆变器和DC/DC转换器、电源管理和分断设备(如固态断路器)、用于直流微电网的DC/DC转换器1以及需要双向逆变器的电池储能系统。

高压碳化硅器件/模块封装的挑战

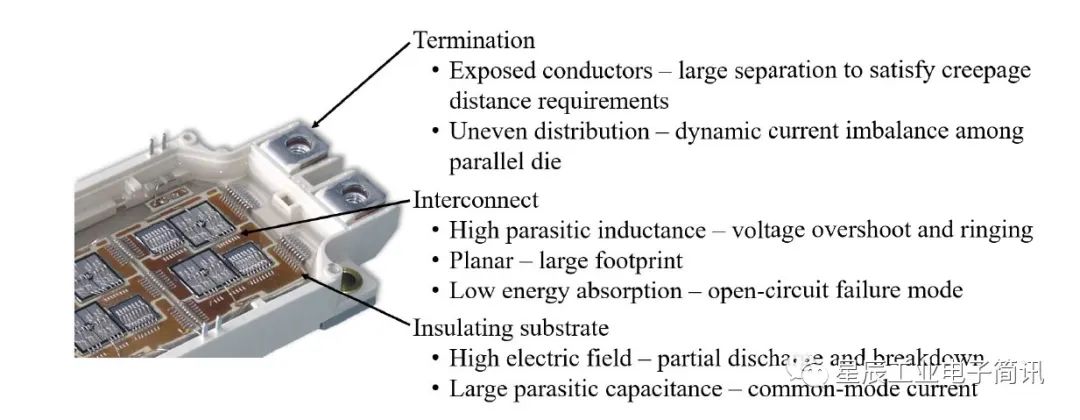

l由于其更快的开关速度,SiC器件对封装中的寄生电感更敏感。这些电感会与器件电容共振,造成不良的电磁干扰。在高速电流瞬变(di/dt)期间,器件上可能会产生较大的过压,这会降低器件可靠性或导致灾难性故障。

l并联器件通常用于实现模块额定电流。寄生电感/电容或静态器件参数(如阈值电压)的不平衡会导致并联芯片上的瞬态电压过冲变化。具有较高过冲的芯片将获得更大的开关损耗,因此温度更高。这会缩短模块寿命。通常添加外部栅极电阻器来控制过冲。然而,这会增加开关时间,从而增加损耗。目前,已经提出了低电感无焊线互连方案,例如,金属柱平行板互连。2去耦电容可用于减轻寄生电感的影响。一种方法是将电容器放置在功率器件上方,形成一个垂直电力环路,使模块占水平位面积保持不变。

l传统的功率模块包括穿过绝缘陶瓷基板(如直接键合铜或DBC)到散热器的寄生电容,散热器通常处于地电位。在较高电压瞬变(dV/dt)下,该电容成为共模(CM)电流流过系统接地的路径。滤波器和扼流圈可以缓解这种情况。但是,它们会增加成本和复杂性。可以使用多层陶瓷基板添加屏蔽层,将CM电流返回芯片,同时降低高频噪声。

l这些高压器件中产生的高电场可能超过封装中介电材料的击穿强度。这会产生局部放电(PD),从而损坏绝缘陶瓷基板。减少电场,从而增加绝缘基板附近的PD起始电压(PDIV)是关键,因为这通常是PD发生的地方。

图1显示了上面讨论的一些挑战。

图1:功率模块封装的挑战

高功率密度、高速10kV功率模块封装方案

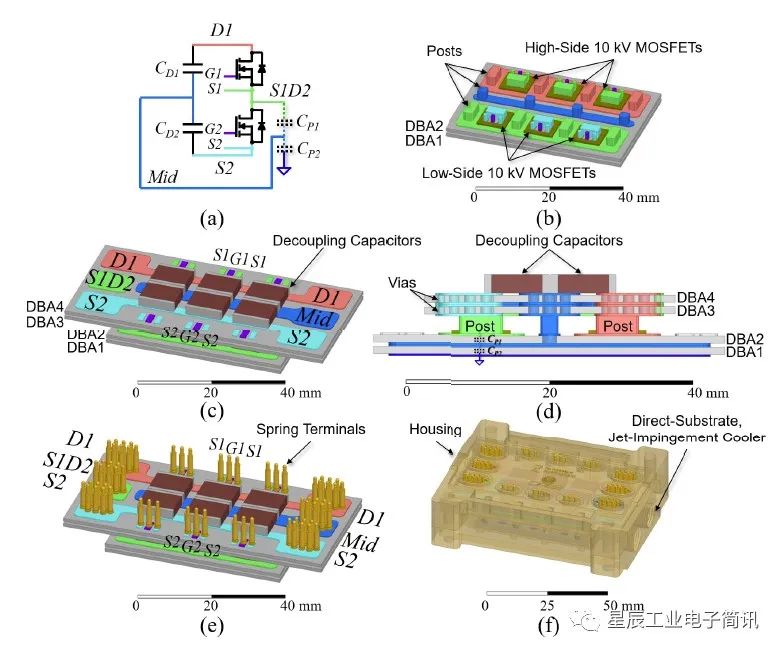

DiMarino在CPES的团队提出了一种创新的封装解决方案,用于10kV,350mΩ SiC功率模块,具有高开关速度,改进的高压性能和更低的CM电流。6还对该拟议封装的关键方面进行了实验验证。图2显示了半桥模块的原理图和3D模型。

图2:拟议的封装——(a)原理图;(b)底部堆叠基板,带有六个10kV MOSFET芯片和柱子;(c)带有嵌入式去耦电容器的顶部堆叠基板;(d)显示通孔和PCB的侧视图;(e)带弹簧端子的模块;(f)带集成式直接基板冷却器的外壳

下面讨论其一些主要设计和结构特性:

l半桥模块每支路具有三个10kV碳化硅MOSFET。不使用外部反并联二极管。SiC MOSFET 体二极管的显著改进可实现对称反向传导和低恢复损耗。7

l模块尺寸为74 ×49 × 11mm(不含外壳),功率密度为13W/mm3。增加的外壳和集成的冷却器使净功率密度达到4W/mm3。

l在功率模块中,电场集中在陶瓷、金属和封装的交点,5被称为三关键点。堆叠DBC基板可以减少块状陶瓷内和关键三点处的电场。8当低边开关导通时会产生最恶劣情况的电场。对这种条件下的电场仿真得出结论,在堆叠陶瓷方法中,中间金属层应连接到直流母线电压的一半,即在这种情况下为5kV。与单基板相比,峰值电场减少了58%,并且均匀分布在两个块状陶瓷基板内。创建半总线的实现是通过一对5kV陶瓷去耦电容完成的,如图2(c)所示。电容器的5kV中点连接通过金属柱和过孔完成,如图2(d)所示,并连接到底部DBA堆栈的中间金属层。所提出的模块具有平面夹层结构。如图2(d)所示,使用了四个基板,芯片下方有两个(DBA1,DBA2),上面有两个(DBA3,DBA4)。堆叠基板方法有效地提高了PDIV。开发了一种压力辅助银(Ag)烧结工艺,用于粘合50×50毫米底部和35×75毫米顶部堆叠基板。与焊料相比,银烧结具有低空隙含量、更高的导热性和可靠性以及经历多次烧结循环而不影响先前烧结接头的能力。印刷浆料涂覆干燥后,在液压机中施加1MPa的压力,温度升至260°C进行烧结。基板在均匀压力下冷却,以防止铝(Al)和氮化铝(AlN)之间的CTE不匹配弯曲或开裂。测得的线热阻为0.11–0.14K/W,表明具有良好的均匀性。

l由钼(Mo)制成的金属柱用于增加距离,从而减少芯片和顶部基板之间的电场。选择Mo是因为其低CTE。对后附着尝试了无压和压力辅助银烧结方法,在粘合强度方面产生了类似的结果。最佳柱高是电磁和静电性能之间的权衡,较短的柱子可降低寄生电感和电阻,但会增加电场强度。该场需要低于封装材料的击穿强度。电场分布的仿真表明,当柱子高度从1mm增加到2mm时,电场显着降低;因此,选择了2毫米的高度。

l图1(a)所示的S2D2节点在D1和S2之间切换时会经历高dV/dt。为了将系统接地处产生的电流转移回直流母线,9堆叠DBC排列中的中间金属层可以连接到正极或负极总线。分流回的电流量将取决于连接回直流母线的高频阻抗。因此,此CM屏蔽的实施至关重要。将中间金属层连接到去耦电容器的中点可为CM电流创建低电感路径,平衡并降低MOSFET开关对的功率环路电感,并降低三关键点处的峰值电场。

l所得模块的电源环路电感为4.4nH/MOSFET对,10这是迄今为止报告的10kV SiC功率模块的最低值之一。

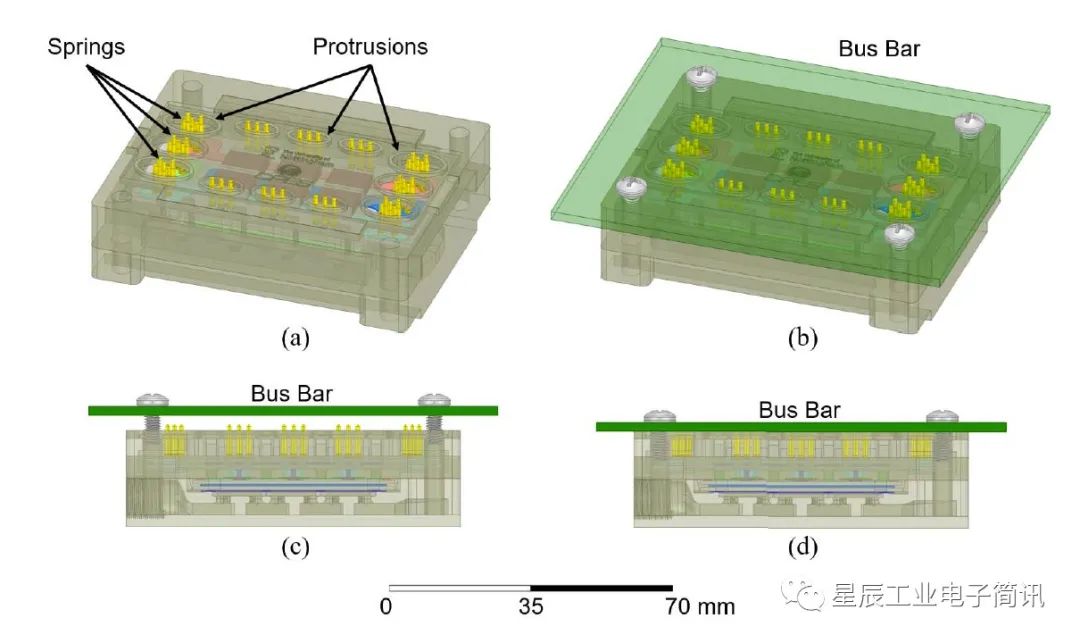

l外壳对整体尺寸、热阻和额定电压有重大影响。图3显示了外壳设计。外部母线安装在顶部,并通过安装螺钉施加压力。压力压缩弹簧,直到母线接触外壳盖中的突起。由于弹簧未暴露,因此爬电距离和间隙限制不适用。突起在外壳盖和母线之间形成明确的气隙,可以对其进行调整以权衡PDIV和附加连接距离的寄生电感/电阻。较大的间距将增加PDIV和寄生效应。这里选择了1毫米的突出高度。即使如此,如图4(a)中的电场仿真所示,电场强度也超过了空气中3kV/mm的击穿。因此,提出了母线内的场控板,其电位与弹簧端子相同,用于将峰值电场从空气转移到母线内的固体绝缘,如图4(b)所示。

图3:外壳设计—(a)带外壳和盖子的模块;(b)带母排的模块;(c)模块的侧视图;(d)带有压缩弹簧端子母排的模块

图4:电场分布仿真—(a)没有和(b)在母排PCB内有场分级板

l用于冷却的底板和导热硅脂会增加净热阻,并在陶瓷基板上产生弯曲应力。在所提出的封装中,底部DBA匹配到外壳上,并使用有针对性的喷射冷却系统,该系统将冷却液直接注入基板的下表面。

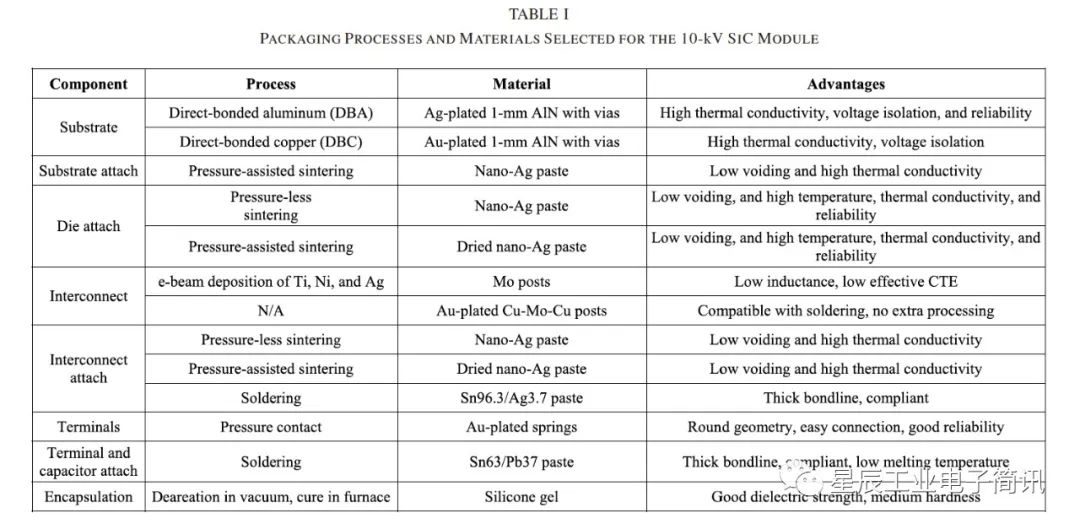

l芯片贴装选择银烧结是因为与焊料相比,银烧结的热阻和热循环能力较低。由于10kV SiC MOSFET芯片具有金(Au)背面金属化,并且银的扩散速度快于金,因此需要烧结曲线来限制银扩散并防止空隙形成。因此,本研究使用230分钟时90°C。平均抗剪强度达到15MPa。施加压力可以将其提高到约25MPa,但在同时烧结多个芯片时会增加复杂性。

l构建了一个原型模块,其中使用的弹簧具有10A的连续额定电流。外壳和集成的喷射冷却器由高温树脂3D打印而成。选择低粘度的硅凝胶进行填封,因为它加工简单,可靠性好,气穴少。

表1列出了为模块原型选择的工艺步骤和材料。

表1:为10kV SiC模块选择的封装工艺和材料

原型模块测试结果

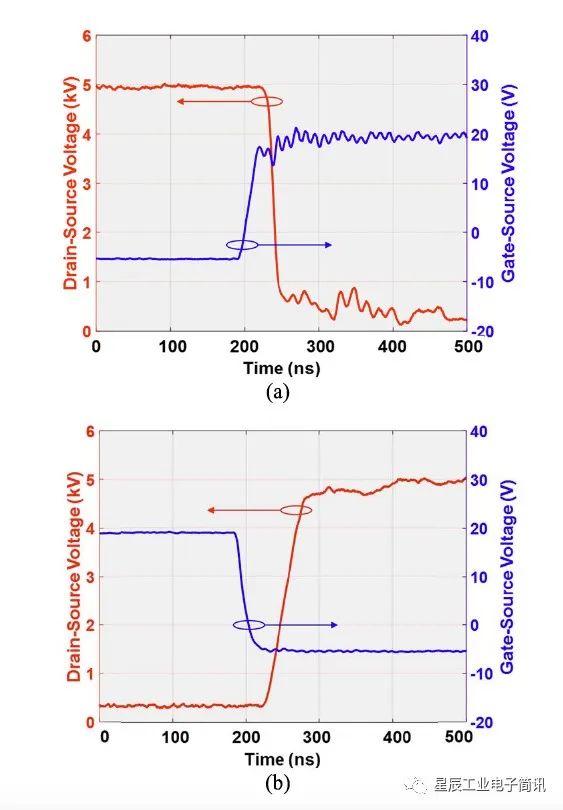

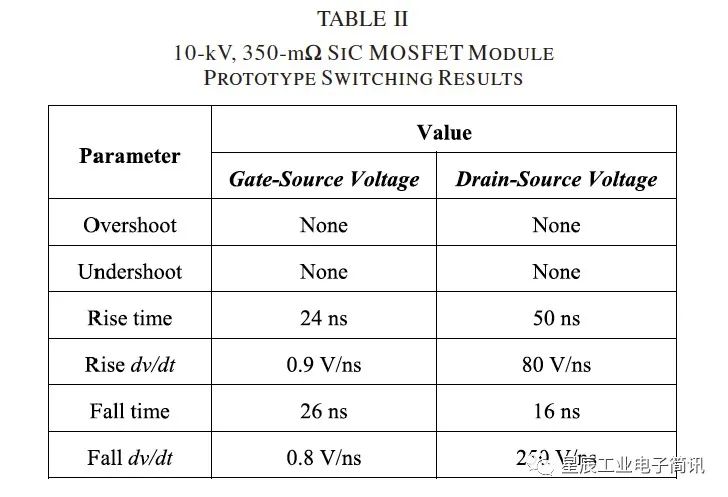

图5显示了使用两个SiC 10kV MOSFET进行双脉冲测试时模块的开关性能。测试在5kV 和20A下进行,导通和关断栅极电阻分别为0.33和0.17Ω。表2列出了此测试的瞬态参数。观察到的过冲和振铃可以忽略不计,表明栅极环路和源极环路电感较低。这些结果是类似额定值的SiC MOSFET和IGBT报告的最快开关速度。

CM屏蔽的有效性是在带宽为200 MHz的接地路径中使用RF电流互感器测量的。图6显示了三个MOSFET并联时的关断波形。在25kV母线电压下,dV/dt为2V/ns。如图所示,CM屏蔽将接地电流过冲从2A降低到0.2A,验证了其有效性。

图5:10kV模块原型的开关波形

表2:10kV、350mΩ碳化硅MOSFET模块原型开关动作实验结果

图6:关断时带和不带CM屏蔽的接地电流波形

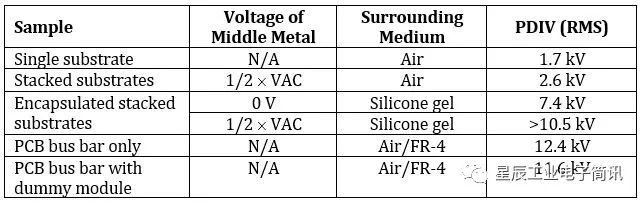

PD测试使用50kV、60Hz交流激励源和PD传感器进行。这些测试在内部堆叠基板以及具有内部场分级的PCB母线上完成。使用图案化的1mm厚AlN-DBA衬底,金属走线间距为2mm,用于比较单个基板与堆叠基板,其中中间金属处于施加电压的一半。

如表3所示,与单基板外壳相比,当中间金属连接到施加电压的一半时,堆叠上的PDIV在空气中增加了53%,在封装中增加了>40%。带有内部场分级板的PCB母线也使用PD测试进行了验证。如表3所示,母排在空气中的PDIV为12.4kV,在空气中的PDIV为11.6kV,在母排上安装了一个PD假模块。

表3:PD测试摘要

原型模块的热特性显示,结到环境比热阻最低,为26mm2·K/W (0.38K/W)。11

总之,DiMarino说:“在CPES,我们提出了一种用于10kV SiC MOSFET的高功率密度、高速模块封装,可用于各种MV功率转换和配电应用。我们的封装方法侧重于低寄生效应、降低共模电流、实现高局部放电电压和降低热阻。有了这个,我们可以真正利用卓越的SiC材料特性,在这个电压等级中创建高效的解决方案。

SiC MOS

更多信息请关注

微信公众号

邮箱:ymq@mgmsemi.com

深圳:深圳市光明区光明街道华强科技生态园5A栋1216

成都:成都市高新区双柏路68号汇创天下科技园西区1栋9层907

长沙:长沙市岳麓区麓谷科技创新创业园A1栋2404

上海:上海市闵行区万源路2161弄150号1号楼318

菲律宾:12 Ibayo St, Manila, Metro Manila, Philippines