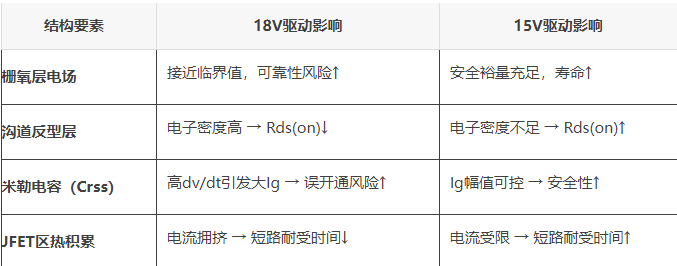

碳化硅MOS驱动电压选择15V还是18V,是电力电子设计中的关键权衡问题。这两种电压对器件的导通损耗、开关特性、热管理和系统可靠性有显著影响。那为什么有15V和18V两种驱动电压呢?他们的差异到底在哪里?今天我们就一起来学习一下。首先是栅极氧化层(Gate Oxide)的电场应力差异。SiC MOS的栅氧化层通常采用SiO₂,但其临界击穿电场强度(约10 MV/cm)远低于SiC材料本身(>30 MV/cm),成为器件可靠性的瓶颈。栅氧厚度:典型值50-100 nm(与硅基MOSFET相当),但承受电压能力不同。18V驱动的碳化硅MOS,栅极电场强度 ≈ 3.6-7.2 MV/cm(按100-50nm氧化层计算);15V驱动的碳化硅MOS,栅极电场强度 ≈ 3.0-6.0 MV/cm。在可靠性方面:18V驱动接近SiO₂临界值(8-10 MV/cm),长期高压加速氧化层老化,引发福勒-诺德海姆隧穿(F-N Tunneling),导致Vth负漂移,而15V驱动的安全裕量提升20%,显著降低栅氧退化风险,高温下(>175°C)电荷 trapping 效应减弱。18V驱动使栅极电场强度提升20%,直接牺牲长期可靠性换取瞬时性能。沟道反型层(Inversion Layer)的导通特性SiC的低沟道迁移率(仅为硅的1/10)是核心瓶颈,需更高垂直电场才能形成低阻通路。

元胞设计:平面栅(Planar)或沟槽栅(Trench)结构影响电场分布。

另外:高温(>150°C):SiC价带激活能降低,15V驱动下沟道导通能力进一步恶化,而18V驱动可补偿此缺陷。低温(<25°C):15V驱动可能因阈值电压(Vth)升高导致导通不充分,18V优势更显著。

寄生电容(Ciss, Crss, Coss)的开关行为差异

SiC MOS的高掺杂漂移层与薄基区设计导致寄生电容非线性特性突出:米勒电容(Crss):栅漏电容C_gd在高压下急剧减小(因耗尽层展宽)。

18V驱动:dv/dt↑ → Crss容抗↓ → 栅极电流Ig = Crss×dv/dt 剧增,高Ig易抬升Vgs超过Vth,需负压关断抑制;

15V驱动:dv/dt较低 → Ig幅值减小,米勒平台电压更低,寄生导通概率下降30%。

新一代器件(如ROHM双沟槽栅)通过屏蔽栅设计降低Crss,但18V驱动仍需-5V关断电压保障安全。

我们应该如何选择呢?

选18V驱动的结构及应用场景:

架构上:采用屏蔽栅/双沟槽等低Crss结构(如Wolfspeed Gen4);系统散热极佳(如液冷),可快速转移JFET区热量;氧化层工艺升级(如氮化退火SiO₂)。

应用场景上:

高频高功率系统:如光伏逆变器、车载OBC,需最小化损耗提升效率;

有限流电感的拓扑:如LLC谐振转换器,短路电流可控,抵消抗短路弱点;

低温环境:结温<150°C,避免Vth漂移问题(如数据中心电源)。

选15V驱动的结构及应用场景:

结构上:传统平面栅结构(Cree Gen2/Gen3);高温应用(>150°C)或氧化层厚度>70nm;无限流能力的拓扑(如Buck-Boost)。

应用场景上:

高可靠性需求:如工业电机驱动、电网设备,需长抗短路时间;

高温或无限流拓扑:结温≥175°C或Buck电路等,依赖驱动电压保障安全;

兼容性优先:改造现有Si IGBT系统,避免重新设计驱动电源。

在驱动设计方面需要考虑的因素:

负压关断的必要性

18V驱动因高dv/dt风险,必须搭配负压关断(-3V~-5V)或米勒钳位功能。

15V驱动在低dv/dt场景可尝试0V关断(如英飞凌CoolSiC™),但需实测验证。

驱动芯片与电源要求

18V驱动需支持高CMTI(>100V/ns)、轨到轨电压(如+20V/-5V),电源设计复杂。

15V驱动可用标准±15V隔离电源,降低成本(如三菱电机SiC模块)。

短路保护响应时间

SiC MOSFET短路耐受时间仅2-4μs(IGBT为10μs),18V驱动要求保护电路响应<1.5μs,需专用驱动芯片(如英飞凌1ED38X0系列)。

选择15V还是18V本质是效率与鲁棒性的取舍:

选18V:追求极致效率,接受更高的保护电路成本与可靠性风险;选15V:侧重系统稳定性与兼容性,容忍适度损耗增加

终上:选择时参考具体器件手册的Rds(on)-Vgs曲线与短路耐受曲线,结合结温、拓扑结构、保护电路能力综合决策。高频场景优选18V+负压关断;高温/高可靠场景首选15V+米勒钳位。