明古微半导体

MGME SEMICONDUCTOR

碳化硅功率器件+电驱方案

新能源汽车.充电桩.工业电源.光伏储能.电力电子.低空飞行器...

国产碳化硅 就找明古微

技术学院

STUDY

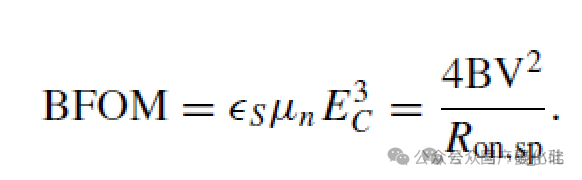

Wide Bandgap Semiconductor(WBG),宽禁带半导体,典型代表包括SiC和GaN,相比Si,WBG材料具备更高的临界击穿场强和更高的热导率,材料优势使其能够实现更高耐压、更低导通电阻。

人们在1990年代投入大量资金,致力于制备直径更大、微管密度更低的SiC晶圆,1992年,Baliga等人报道,首款高压(400 V)6H-SiC肖特基整流器(SBD)问世,导通压降仅为1.1 V,且与Si PIN整流器相比,无反向恢复电流。

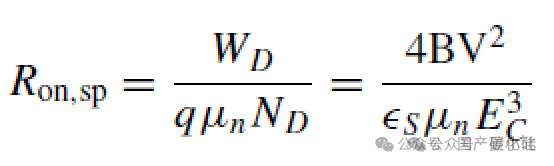

1994年,Baliga等人以BFOM为指标,量化了SiC器件的优势,预测相比Si器件,其可以将Ron,sp降低3个数量级,当然,那时的学者并不能预测30年后,SiC器件的沟道迁移率问题尚未得到有效解决。

1997年,Baliga等人报道,6H-SiC ACCUFET(Accumulation-mode FET,积累型MOSFET)问世,这是SiC材料制备的首款功率MOSFET。

1998年,Baliga等人报道,用4H-SiC、6H-SiC材料,分别制备ACCUFET,进行对比。这是4H-SiC材料制备的首款功率MOSFET。

这些早期的概念验证,激发了全球范围对SiC功率器件的研发,美国、日本和欧洲等地相继开展相关研究。

这要从大名鼎鼎的仙童半导体说起,1958年6月,戈登·摩尔(提出摩尔定律的那位)带领的小组,率先开发出硅基商用NPN晶体管,业界震惊,订单源源不断,仙童公司的前景一片光明。但在1958年行将结束之际,高层察觉到阴霾正在逼近——越来越多的客户投诉仙童的硅晶体管不稳定。代号“UFO”的小组成立,在摩尔的带领下,调查原因。

工程师发现,只要轻轻敲击外壳,晶体管就可能失效,解剖后发现,原来是金属壳内壁的金属屑掉落到PN结上,引发短路。初步解决方案,是改善产线洁净度,减少颗粒,但效果甚微。仅从生产的角度,很难解决这个问题。也许要从器件结构入手。

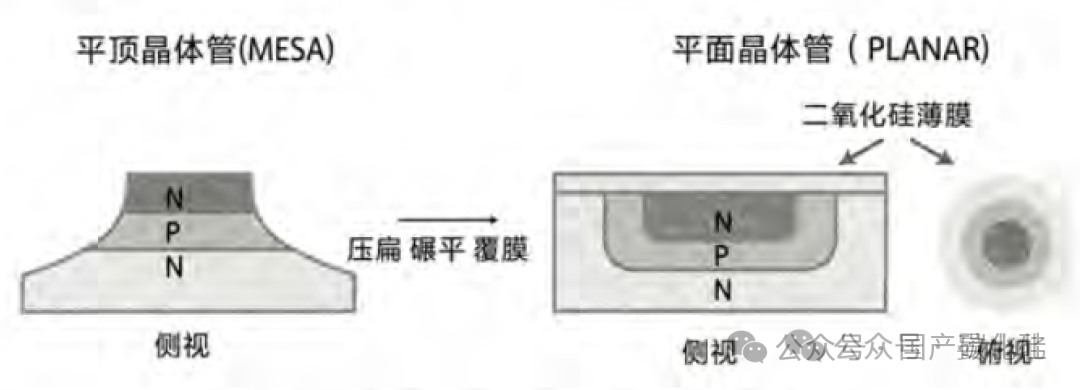

图片来源:网络

琼·霍尼解决了这一问题,他的方案,正是今日我们早已习惯的平面晶体管(planar transistor)。左图为仙童此前采用的平顶晶体管(mesa transistor),右图为霍尼提出的平面晶体管。自上而下,依次为发射极、基极和集电极。两者的核心差异,在于半导体材料的完整性,平顶晶体管,就像一座火山,顶部窄而底部宽,类似“凸”字造型,而平面晶体管,是一块方方正正的半导体材料,表面覆盖一层二氧化硅薄膜。

平顶晶体管的全称,应为硅双扩散台面晶体管(Double-Diffused Silicon Mesa Transistor),大概工艺流程是:

1)准备一片轻掺杂N型硅片,作为晶体管的集电区(Collector)

为什么要进行台面腐蚀?

然而平顶晶体管的问题在于,发射结和集电结的侧壁裸露于空气中,容易吸附颗粒,降低器件可靠性。这是器件结构的固有缺陷,难以通过生产管控降低。

而霍尼的想法,是将这座火山彻底压扁,让顶部较窄的平台,陷入山脚。

如果从俯视视角观察,该结构是一个同心圆,从内到外,依次是发射极、基极和集电极。完成扩散后,于半导体材料表面覆盖一层SiO2薄膜,不让PN结与外界颗粒直接接触。

如此,便从器件结构的角度,彻底解决了PN结裸露带来的可靠性问题。

1959年3月,第一只平面晶体管被制造,经测试,可靠性远胜平顶晶体管,客户对此非常满意。

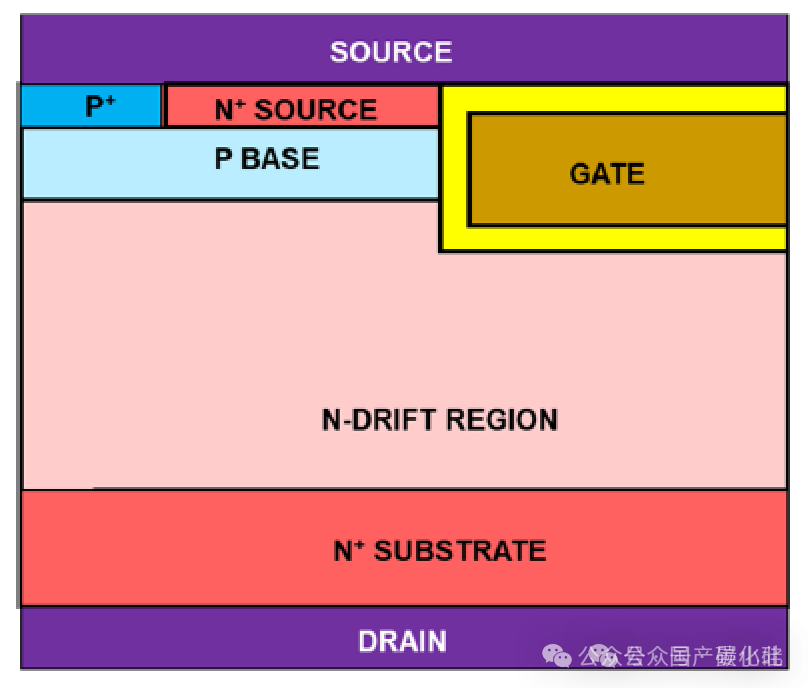

然而不知各位是否意识到,当年的平顶晶体管,与沟槽型功率MOSFET,是不是结构神似?后者在两侧的“空洞”中,填有栅介质和栅极材料而已。将历史发展与如今器件相映证,别有一番趣味,说回SiC planar MOSFET:

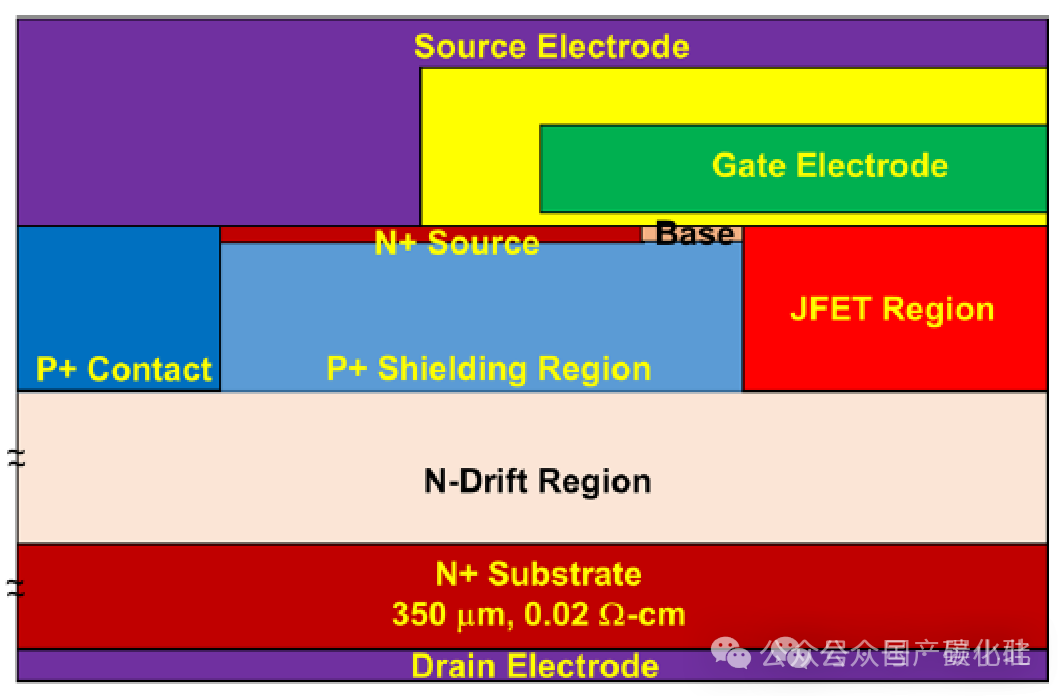

图片来源:网络

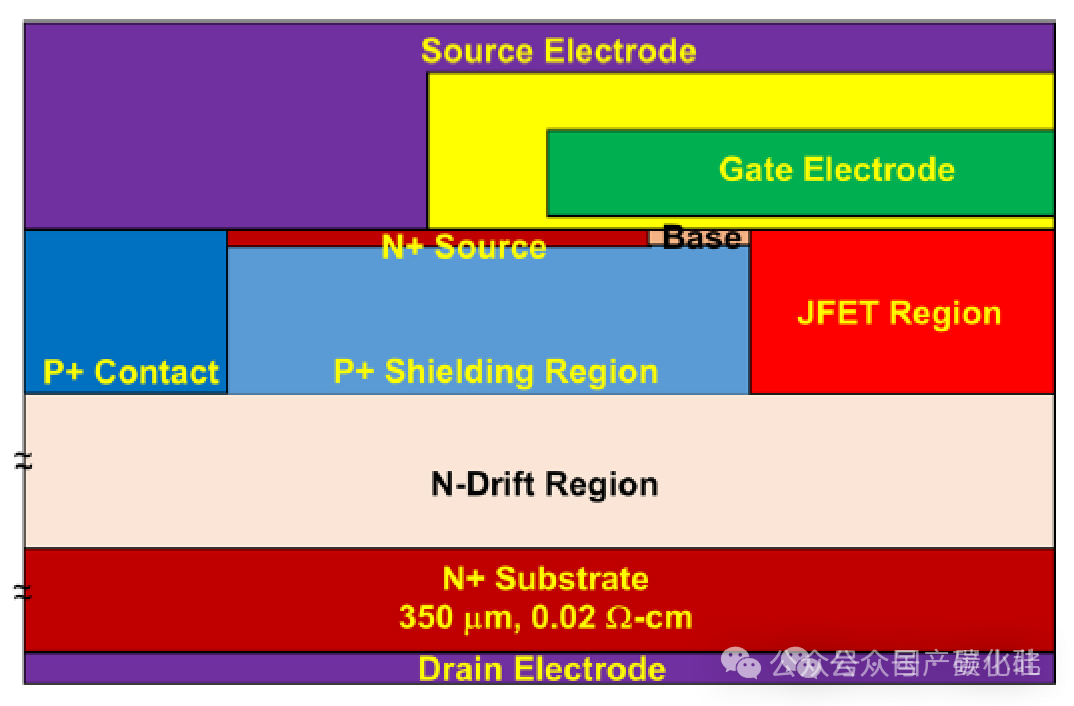

如上,SiC Planar MOSFET基本结构,对Si VDMOS(Vertical Double-diffused MOSFET,垂直双扩散MOSFET)而言,核心工艺是——通过高温热扩散形成P-body和N+源区(双扩散),从而精确控制沟道长度。

但SiC器件无法沿用扩散工艺,原因是常用杂质在SiC材料中的扩散系数极低,换言之,欲实现类似的扩散深度,所需的温度远高于栅极材料多晶硅所能承受的温度。

解决方案,是离子注入工艺。

通过某些方式,使P-base和N+源区的注入掩膜边缘分离,以此定义沟道长度。从这里也能看到两种称呼的区别,

目前的商用SiC MOSFET产品,都是反型器件,即,Base区是P型掺杂,正向导通状态下,通过栅压的变化,促使Base区表面载流子类型反转,变成N型,以建立电流路径。

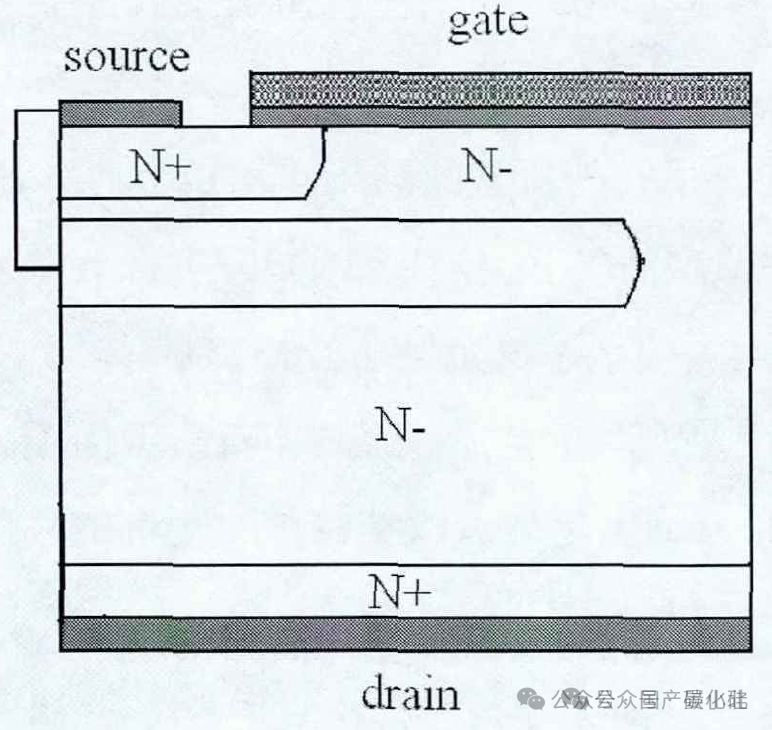

图片来源:网络

但三十年前,业界刚开始研究SiC MOSFET时,多从积累型器件入手,即,Base区是N型轻掺杂,如上,可以看到,gate和栅氧下方区域是N-,而非P-base,N-下方有一横向延伸的P区,

通过调整N-区、P区参数,确保栅压为0时,N-区完全耗尽,以实现常关功能,栅压为正,在N-区表面形成积累型沟道(N-区中电子为多子),从而连接源漏。

为什么先研究积累型器件?

1)P区对栅氧的保护效果较差,栅氧可靠性存疑,

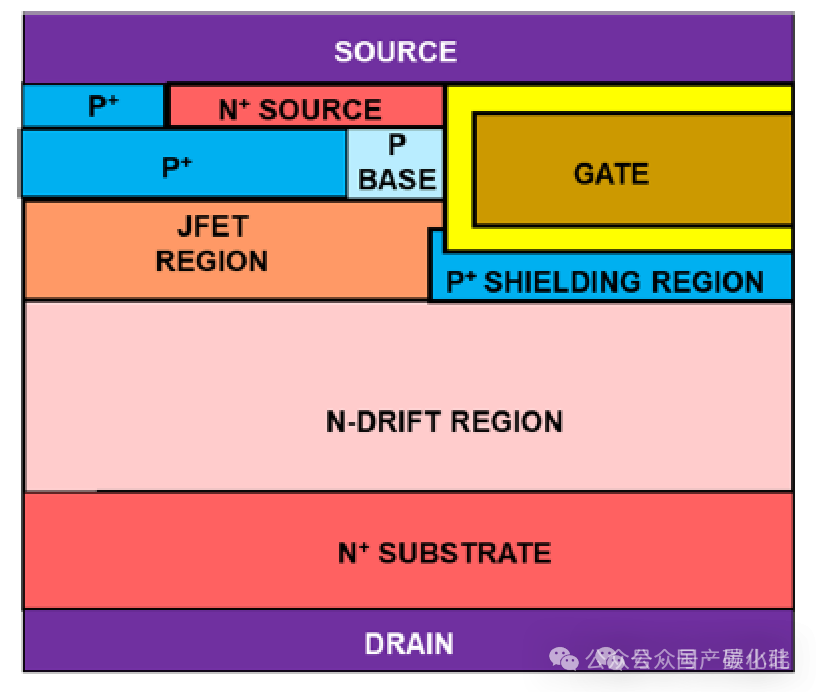

看第一张图,有一P+ shield区,这是SiC平面MOS的独特之处——它不能简单复制Si VDMOS的结构设计。

图片来源:网络

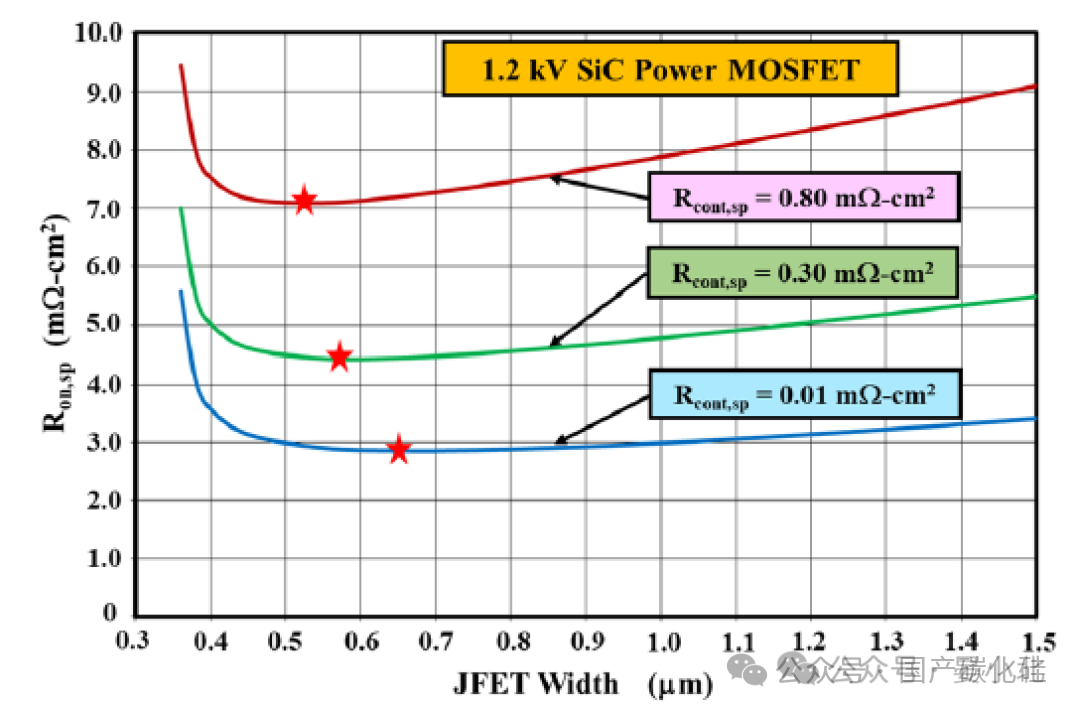

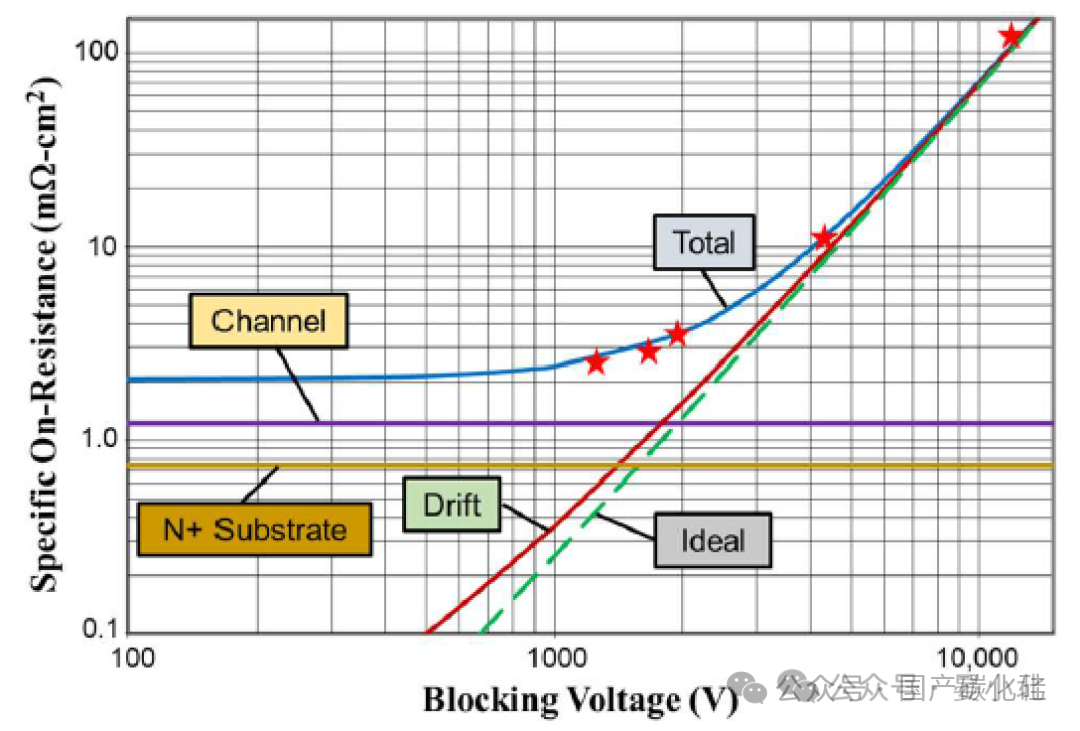

这张图强调了N+欧姆接触电阻的重要性。

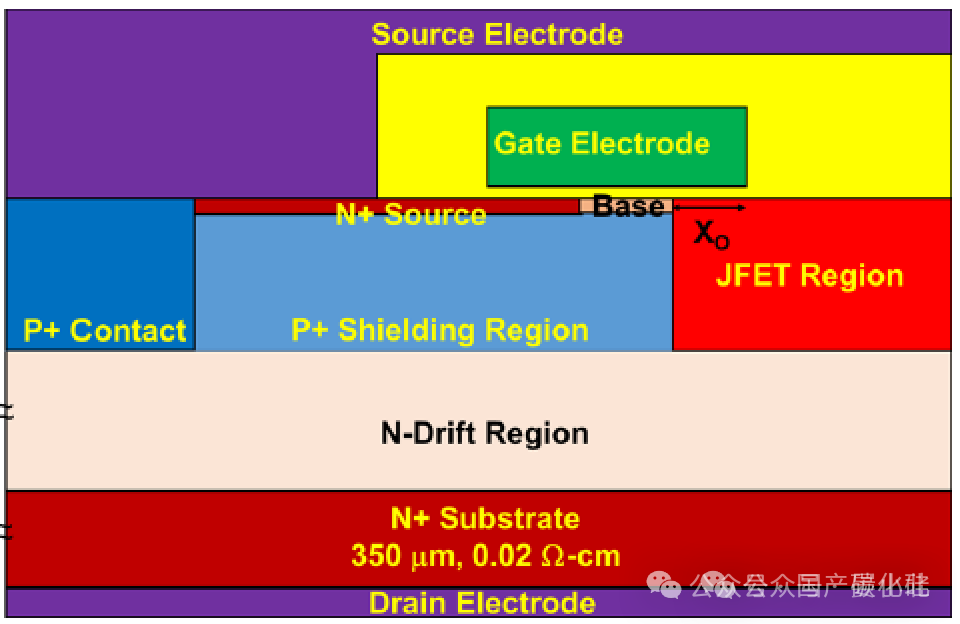

建立1200V SiC MOSFET模型,元胞尺寸2.8μm,沟道长度0.5μm,欧姆接触宽度1.5μm,漂移区浓度8e15 cm−3,厚度10 μm,沟道迁移率调至16 cm²/V·s,栅氧厚度50 nm,该模型下,器件BV为1650V,Vth为2.5V,350μm厚、电阻率0.02 mΩ·cm的N+衬底对总电阻的贡献为0.7 mΩ·cm²,通过改变JFET宽度,可优化器件总电阻。

三条曲线,代表三种N+接触电阻下,器件总电阻的差异,随着N+接触电阻从0.01 mΩ·cm2升至0.8 mΩ·cm2,器件的最优Ron,sp从2.8 mΩ·cm2增至7.1 mΩ·cm2,恶化明显。且,根据N+接触电阻的不同,器件最优电阻对应的最佳JFET宽度也有所差异(三个星号对应的横坐标)。

0.01 mΩ·cm2的N+接触电阻,可通过1000°C高温欧姆退火实现,而0.8 mΩ·cm2的N+接触电阻,出现在900°C欧姆退火后。

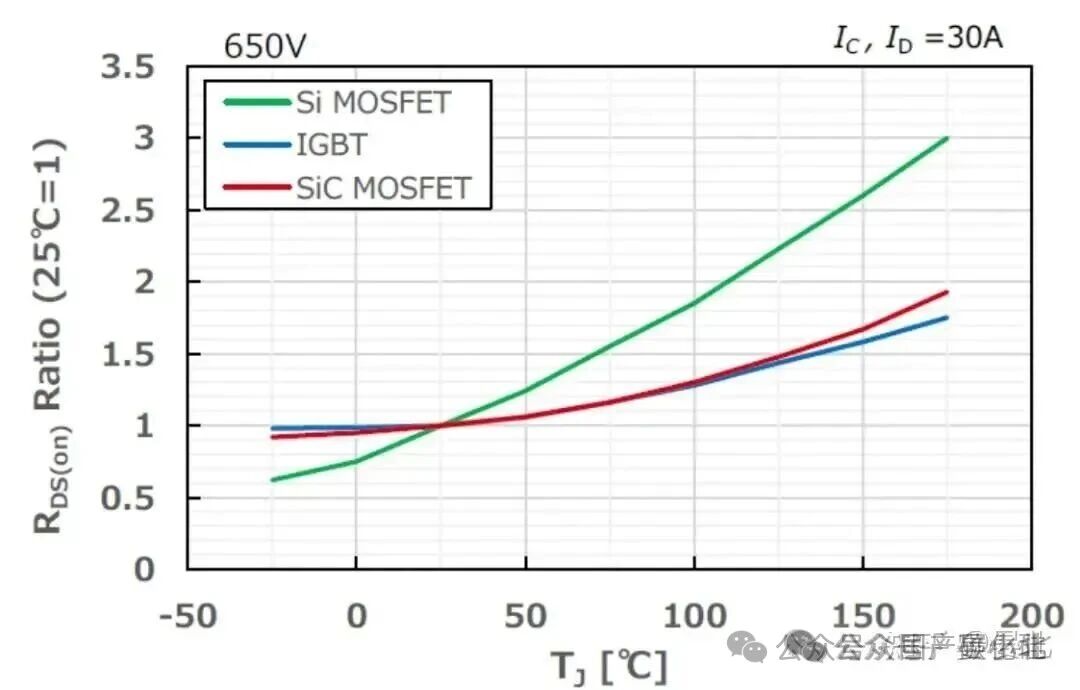

再说沟道电阻和漂移区电阻,提一个问题,SiC MOSFET导通电阻的温度系数,在不同结构设计、不同工作条件下,到底如何变化?

有两个变量,结构设计or工作条件,前者,决定沟道电阻和漂移区电阻的占比,这两部分电阻是SiC MOSFET导通电阻的主要成分,且二者的温度系数有明显区别。

图片来源:网络

这张图,是650V SiC MOSFET、Si MOSFET以及Si IGBT归一化电阻的温度特性,以0℃到150℃为例,可以看到,Si MOSFET的电阻变化情况最明显,正温度系数最大,为什么相比Si MOSFET,SiC MOSFET的正温度系数更小?

图片来源:网络

这张图,给出SiC Planar MOSFET总电阻、各成分电阻随BV的变化关系,星号表示2014年最先进的SiC MOSFET技术。

图片来源:网络

先回顾平面型SiC MOSFET结构,如上,绿色的栅极(导体)被黄色的栅介质(绝缘体)包裹,位于红色or蓝色的半导体材料之上,栅极区域,半导体材料表面平整,此即平面型。

1990年代,为进一步降低导通电阻,功率半导体行业从Si平面栅功率MOSFET过渡到Si沟槽栅MOSFET。

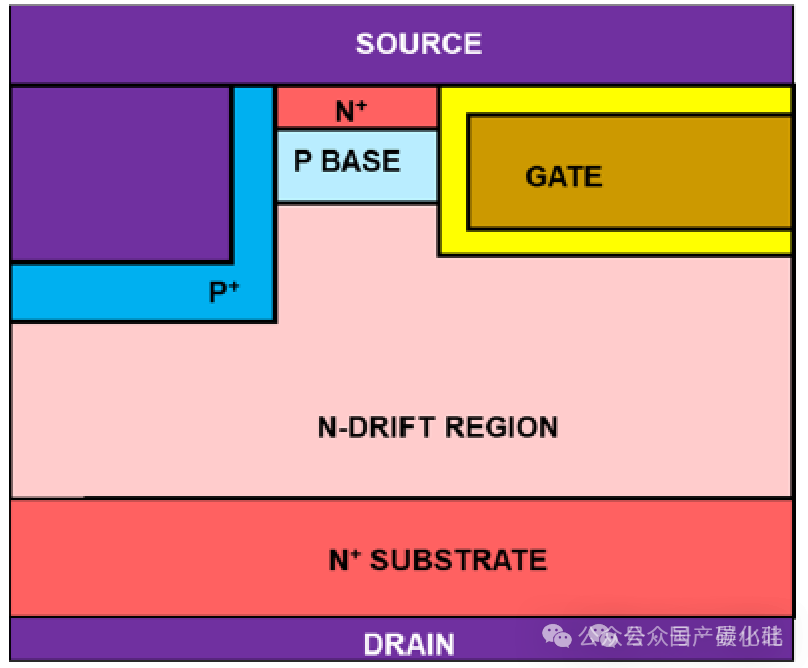

最初,业界试图直接复制Si沟槽栅MOSFET结构,以制造沟槽型SiC MOSFET,

图片来源:网络

器件结构如上,棕色的栅极(导体)被黄色的栅介质(绝缘体)包裹,二者位于红色or蓝色的半导体材料之间,换言之,在半导体表面,隔一段距离挖一个沟槽,向其中填充栅介质和栅极材料,此即沟槽栅结构。

当时SiC材料的离子注入工艺尚不成熟,因此采用外延工艺制备P-base和N+源区,这种结构并不适用于SiC材料,原因有二,

1、关断状态下,栅介质承受的电场强度太大,使器件提前击穿。

图片来源:网络

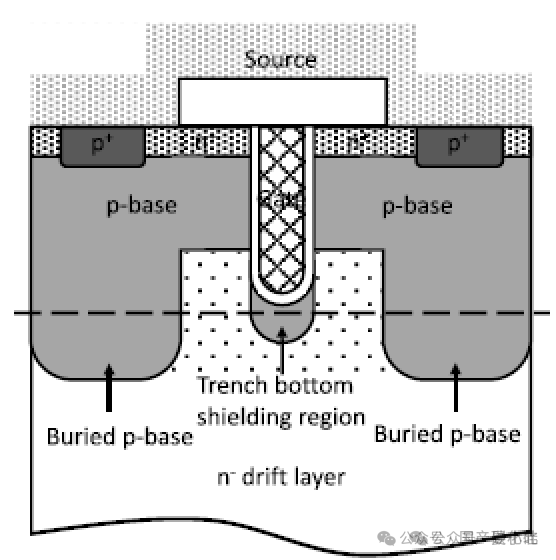

第一种改进结构如上,1995年提出,在沟槽下方设置P屏蔽区,关断状态下利用P屏蔽区与N漂移区形成的PN结,分担电场,以降低栅介质承受场强。

P屏蔽区会增大导通电阻,因此在其两侧设置JFET区,高浓度N型掺杂,确保足够的电流密度。

P-base左侧的P+区用于防止P阱穿通。后来三菱等公司对这种结构有诸多研究,它的最大问题在于,槽底的P屏蔽区如何与源极短接?

图片来源:网络

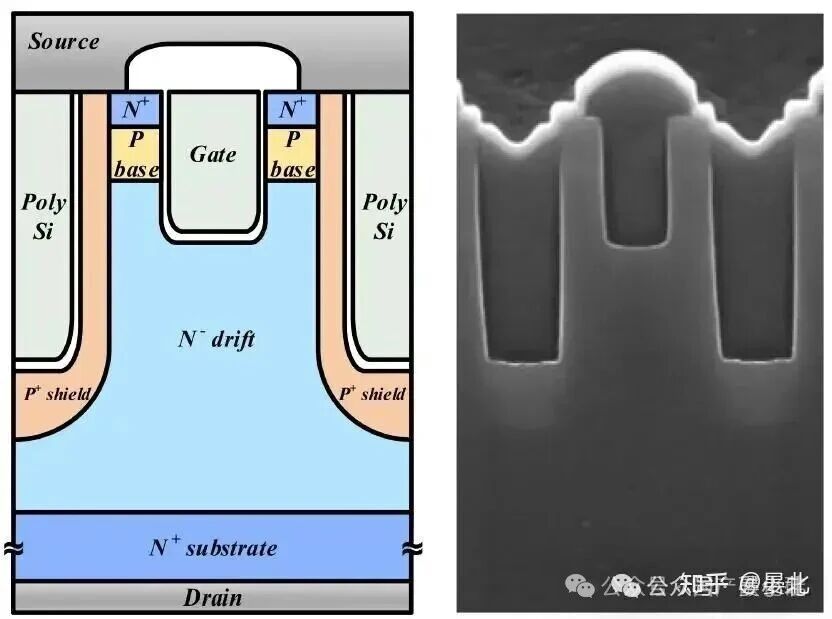

第二种改进结构如上,2011年由ROHM提出,是为DT-MOS,在源极区域和栅极区域同时刻槽,形成双沟槽结构,对源槽的侧壁及底部进行注入,形成P屏蔽区,以此保护栅介质。这张图源槽和栅槽同样深,这是ROHM第三代SiC MOSFET产品的设计:

图片来源:网络

在第四代产品中,源槽深度远大于栅槽,以提供更优异的保护效果。亦有研究证明,如此设计可以显著提升器件的UIS能力。

文献解读——四种商用SiC MOSFET器件UIS能力对比

图片来源:网络

第四种改进结构如上,2013年由丰田提出,特点是:将沟槽底部的栅介质做厚,以提升其抗击穿能力,同时可以降低栅漏电容,提升开关特性。

原报道证明,加厚底部栅介质对导通电阻的影响很微弱,仅增加2%,而Eox降低36%,Qgd降低38%,

图片来源:网络

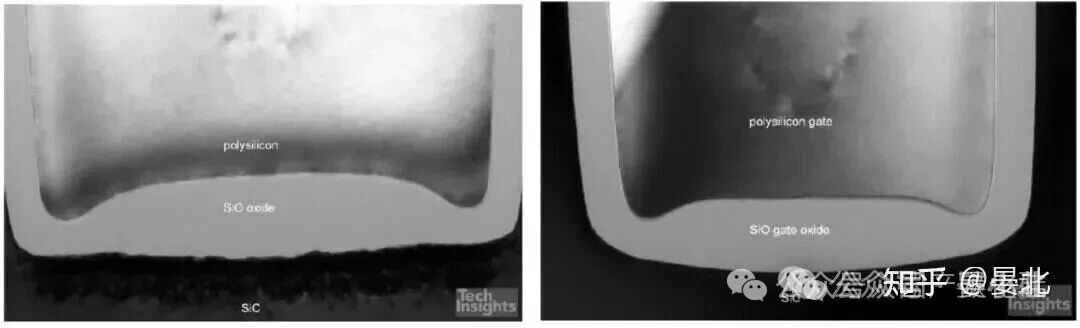

这张图,是ROHM SCT4045DEC11产品的栅槽TEM图像,右图分辨率更高,可以看到,沟槽底部的SiO2层,厚于沟槽侧壁的SiO2层,

不知道ROHM采用的工艺,是否与丰田当年开发的厚介质工艺有关?

图片来源:网络

另一种重要结构如上,2016年的报道,来自AIST,沟槽两侧通过MeV级离子注入,形成较深的Buried P区,以保护栅介质。

这张图中,沟槽底部也设有P区,但为电流密度考虑,很多研究机构不在槽底设P区,只在两侧设计Buried P区,博世等公司对此结构做过大量研究,商用产品亦采用此路线。

(4)SiC MOSFET高频优化方案:聊完常规结构MOSFET,再将目光转向高频领域,即,SiC MOSFET在改善高频品质因数(HF-FOM)领域取得的进展。

何为HF-FOM?这参数为何重要?先解释这个逻辑。

对SiC MOSFET而言,比导通电阻Ron,sp是最常见的参数,因其可以对比不同面积芯片的过流能力,然而Ron,sp并非唯一重要的参数。

SiC MOSFET旨在替代Si IGBT,用于电机驱动逆变器、光伏发电逆变器等场景,相比Si IGBT,SiC MOSFET的一大优势在于更快的关断速度,这源自其单极型器件的固有特性,

但问题在于,SiC MOSFET的成本至少是同等额定值Si IGBT的3倍(2023年数据,2025年据说已有低于Si IGBT价格的SiC MOSFET),但这种成本劣势可以在系统层面得到缓解,原因是SiC MOSFET逆变器工作频率远高于Si IGBT逆变器,而更高的工作频率可减小滤波器等元件尺寸,进而降低系统成本,如此,SiC MOSFET器件层级的成本劣势在系统层级被抵消。

因此结论简单清晰——我们需要保持SiC MOSFET在开关特性上的优势,使其工作在更高频率下,具备更低的开关损耗。这就需要关注动态参数。

开通、关断过程中产生的能量损耗,很大一部分与漏压转换时间相关,而这时间由栅漏电容Cgd(应用层级称之为Crss)、栅漏电荷Qgd决定,减小这两个参数,对提升开关能力至关重要。

于是采用高频品质因数HF-FOM评判器件动静态整体性能,HF-FOM定义为:比导通电阻×栅漏电荷(Ron,sp×Qgd),Ron,sp代表静态功耗,Qgd代表动态功耗,HF-FOM越低,器件整体功耗越低。

接下来,介绍几种优化HF-FOM的方案,包括SG-MOS、BG-MOS和八角元胞,先说SG-MOS(Split-Gate MOSFET,分裂栅MOSFET),所谓SG-MOS,顾名思义,就是将JFET区上方的栅极多晶硅分为两部分,如此设计有何优势?

此前曾经提过,SG-MOS的一种效果,是使JFET区正上方的栅氧厚度明显增大,该结构被用于Si MOSFET,以减轻单粒子效应导致的栅氧损伤,抗辐照分裂栅SiC MOSFET制备而SG-MOS更重要的优势,是提升动态特性,即,通过减小栅漏交叠面积,降低Cgd,进而降低Qgd

图片来源:网络

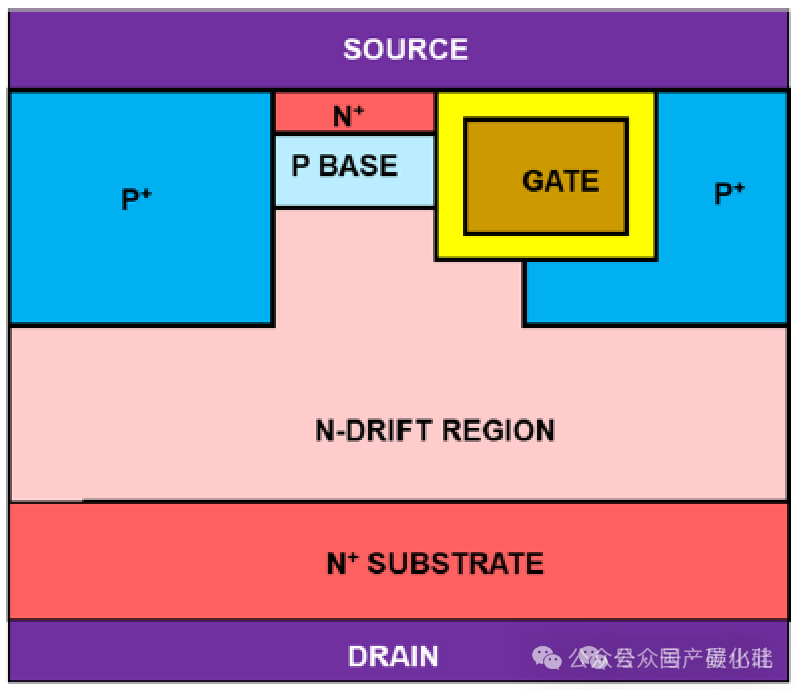

器件结构如上,BG-MOS的特点,是P+屏蔽区延伸至栅极边缘之外,屏蔽电场作用进一步增强,这当然会增大电阻,因此需要在JFET区顶部设置N+ JFET区,以确保电流密度不受明显损失。

另外,P+屏蔽区延伸至栅极之外也有助于减小Cgd,因为P+屏蔽区与源极短接,相当于减小了栅漏交叠面积。

缓冲距离XB是BG-MOS需要优化的参数,已有报道证明,1.2 kV SiC BG-MOS,XB = 0.3μm时,Qgd降低5.8倍,Ron,sp增加1.45倍,HF-FOM降低4倍。

图片来源:网络

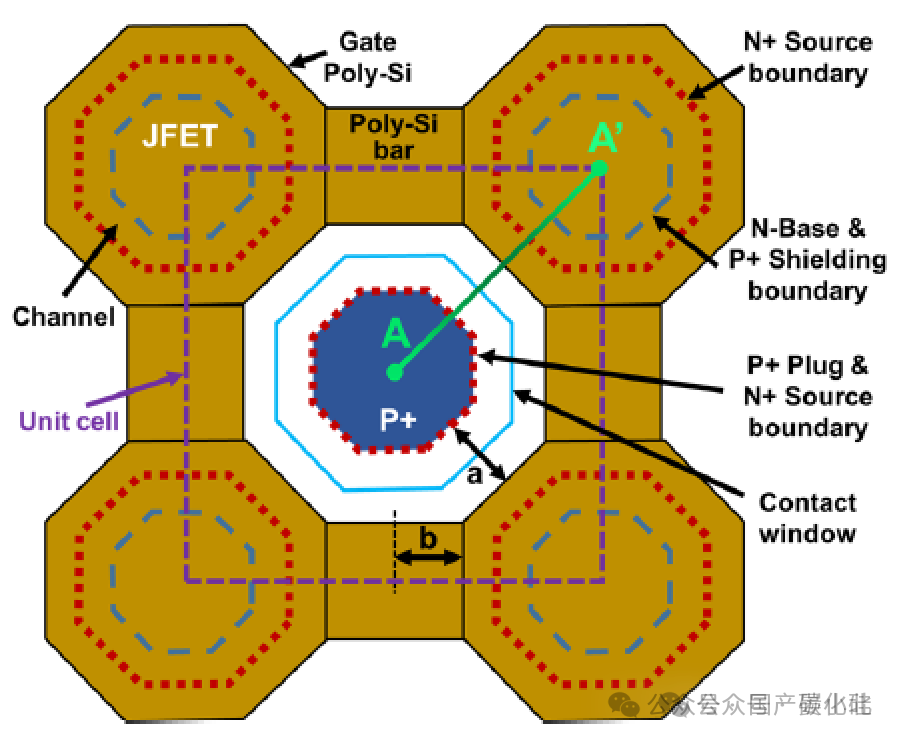

如上,多晶硅、N+、P-shield、P+、JFET、欧姆孔,这几块版都是八角形,相邻八角形多晶硅区域之间,通过矩形多晶硅连接条相连接(Poly-Si bar),多晶硅连接条的长度决定了欧姆接触面积和元胞尺寸,若长度太小,则接触面积太小,不利于制造,若长度太大,则元胞尺寸过大,导通电阻增加。

已有报道同时制备了条形元胞SiC MOSFET和八角元胞SiC MOSFET,对比两者特性,结论是:

1、八角元胞器件的沟道密度明显小于条形元胞器件,这使其导通电阻有一定程度增大

2、八角元胞器件的JFET密度明显小于条形元胞器件,这使其高频特性更优,换言之,相比条形元胞,八角元胞会损害静态特性,提升动态特性,具体参考这篇,八角元胞SiC MOSFET探秘通过参数优化,JFET宽度1.1μm时,相比条形元胞器件,八角元胞器件的HF-FOM可提升1.2倍。

小结

1、材料:相比Si,WBG材料具备更高的临界击穿场强和更高的热导率,材料优势使其能够实现更高耐压、更低导通电阻。

2、材料:BFOM值与EC强相关,为获得更大的BFOM值,需采用更大EC的半导体材料,而EC随着Eg(禁带宽度)的增大而增大,于是业界对宽禁带半导体材料产生兴趣。

3、器件:SiC Planar MOSFET无法沿用Si VDMOS的双扩散工艺,采用离子注入工艺形成P-base和N+源区。

4、器件:SiC MOSFET中,影响器件导通电阻温度系数的主要因素有二,结构设计or工作条件,两者均通过影响沟道电阻和漂移区电阻的占比,影响器件电阻的温度系数。在目前关心的应用范围内,沟道电阻呈现负温度系数,漂移区电阻呈现正温度系数

5、器件:对SiC MOSFET而言,随着器件耐压的增大,外延层逐渐变厚,漂移区电阻占比逐渐增大,导通电阻的温度系数随之增大。

1.7kV以下的中低压器件,欲降低电阻,设计要点在沟道、衬底,1.7kV以上的高压器件,欲降低电阻,设计要点转向漂移区。

6、器件:沟槽型SiC MOSFET的设计关键,就是通过合适位置、合适参数的屏蔽区,分担栅介质电场,确保器件可靠性,同时不至于明显影响电流密度。

7、器件:沟槽型SiC MOSFET五种经典改进结构,包括槽底设置屏蔽区结构、双沟槽结构、不对称屏蔽区结构、底部栅介质加厚结构,以及两侧屏蔽区结构。

8、器件:采用高频品质因数HF-FOM评判器件动静态整体性能,HF-FOM定义为:比导通电阻×栅漏电荷(Ron,sp×Qgd),HF-FOM越低,器件整体功耗越低。

9、器件:SG-MOS是将JFET区上方的栅极多晶硅分为两部分,通过减小栅漏交叠面积,降低Cgd,进而降低Qgd,BG-MOS的特点是P+屏蔽区延伸至栅极边缘之外,且在JFET区顶部设置N+ JFET区,八角元胞器件的沟道密度明显小于条形元胞器件,这会增大器件导通电阻,但八角元胞器件的JFET密度明显小于条形元胞器件,这使其高频特性更优。

国产碳化硅,就找明古微--感谢深圳市明古微半导体有限公司长期对本公众号的赞助与支持,深圳市明古微半导体有限公司作为爱仕特科技碳化硅MOS/SBD、中科本原DSP、乐山希尔整流桥堆/FRD等的核心代理商,与其深度合作并联合开发功率模块及电驱、储能系统,为电动汽车、OBC、DC-DC、充电桩、光伏逆变、SVG、PCS、工业电源、家电变频等能源产业提供完整解决方案,更多信息请登录:wwwmgmsemi.com

SiC MOS

更多信息请关注

微信公众号

邮箱:ymq@mgmsemi.com

深圳:深圳市光明区光明街道华强科技生态园5A栋1216

成都:成都市高新区双柏路68号汇创天下科技园西区1栋9层907

长沙:长沙市岳麓区麓谷科技创新创业园A1栋2404

上海:上海市闵行区万源路2161弄150号1号楼318

菲律宾:12 Ibayo St, Manila, Metro Manila, Philippines