明古微半导体

MGME SEMICONDUCTOR

碳化硅功率器件+电驱方案

新能源汽车.充电桩.工业电源.光伏储能.电力电子.低空飞行器...

国产碳化硅 就找明古微

技术学院

STUDY

在大功率电力电子电路中,当单个 SiC MOSFET 的电压或电流额定值无法满足需求时,工程师常会选择将器件串联分压或并联分流。但实际应用中,即便选用同一批次器件,串联时的电压击穿、并联时的局部过热仍频繁发生。问题根源并非器件质量,而是不可避免的参数偏差—— 从阈值电压到寄生元件,任何细微差异都会在开关动态过程中被放大,最终引发连锁故障。本文结合器件特性与仿真数据,手把手拆解串并联场景下的核心矛盾与解决思路。

1 基础认知:为什么参数偏差会成为 “隐形杀手”?

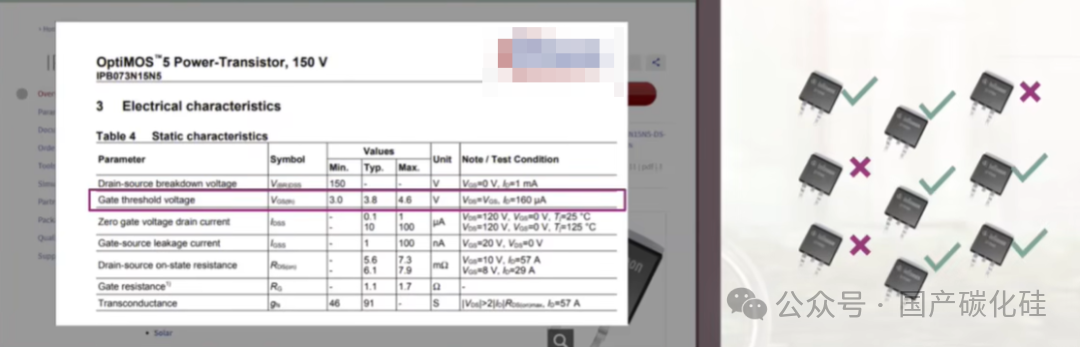

SiC MOSFET 的工作状态由阈值电压(Vth)、导通电阻(Rdon)、寄生电容(CGD、CGS、Coss)、开关速度等核心参数决定。但受制造工艺(如晶圆掺杂均匀性、栅极氧化层厚度)、封装工艺(如寄生电感布局)、驱动电路(如信号延迟、外接栅阻)影响,即使是同一型号、同一批次的器件,参数也存在天然偏差:

阈值电压(Vth)

偏差可能达 0.5-1V,直接影响器件开通 / 关断的触发时刻; 寄生电容

CGD、CGS 的偏差可能达 10%-20%,改变栅极充电节奏; 内部栅阻(RG_INT)

差异会导致栅极电流注入速度不同; 驱动链路

外接栅阻(RG_EXT)、源极电感(LSOURCE)、布线延迟的微小差异,都会打破器件同步性。

这些偏差看似细微,却会导致串并联器件无法 “同频工作”:串联时电压分配失衡,并联时电流分布不均。最终引发三大问题:

器件超额定值

部分器件承受的电压 / 电流超过 datasheet 规定值,直接触发雪崩击穿或热损坏; 损耗不均衡

开关损耗集中在某几个器件上,加剧局部发热; 可靠性下降

长期局部过热会加速器件老化,缩短使用寿命,甚至引发电路宕机。

2 串联场景:分压不均的 “动态陷阱”

SiC MOSFET 串联的核心目标是分压—— 当输入电压(Vin)超过单个器件的额定漏源电压(VDS 额定)时,通过 n 个器件串联,理论上每个器件仅承受 Vin/n 的电压。但实际开关过程中,“动态分压不均” 会让这一理想状态彻底失效。

1. 静态 vs 动态:分压均衡性的 “反转时刻”

静态阶段(无开关动作)

电压按输出电容(Coss)成反比分配。由于 Coss 是器件固有参数,若器件批次一致性较好,此时分压基本均匀,例如两个 Coss 相同的器件串联,各承担 50% 输入电压。 动态阶段(开关动作,尤其关断过程)

分压均衡性被彻底打破。关断时,器件需要从导通状态切换到截止状态,此时开关速度慢的器件会承受更高电压

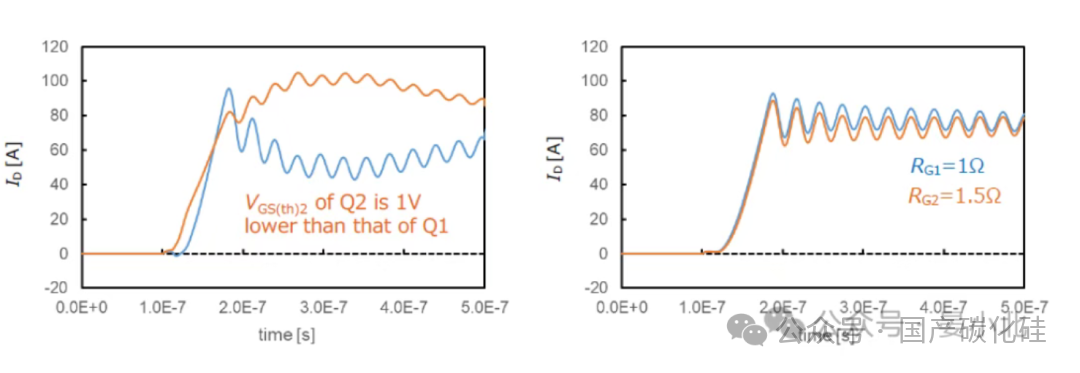

通过仿真可直观看到:当两个串联器件 Q1、Q2 存在 1V 的 Vth 偏差(Q2 的 Vth 比 Q1 低 1V)、0.5Ω 的外接栅阻偏差(RG1=1Ω,RG2=1.5Ω)时,二者的 VDS 波形出现显著差异 ——Q1 的 VDS 峰值比 Q2 高 20% 以上,完全偏离 “均分电压” 的预期。若输入电压接近器件额定值,Q1 的 VDS 很可能超过额定值,引发击穿。

2. 开关速度偏差的 3 大来源

为什么会出现开关速度差异?本质是 “栅极充电节奏不同”,具体由三方面因素决定:

(1)器件自身参数偏差

阈值电压(Vth)

Vth 是器件开始导通的临界栅源电压。Vth 越高的器件,需要更长时间才能达到导通所需的 VGS 电压,开关速度越慢。例如 Q1 的 Vth=4V,Q2 的 Vth=3V,在相同驱动电压下,Q2 会先开通、先关断,而 Q1 因 Vth 高,关断时会 “滞后”,此时电路中的电压会更多转移到 Q1 上。 寄生电容与内部栅阻

CGD(栅漏电容)、CGS(栅源电容)决定栅极充电的 “容量需求”,RG_INT(内部栅阻)决定充电电流的 “流通阻力”。若 Q2 的 CGD 比 Q1 大 20%,则 Q2 的栅极需要更多电荷才能完成充电,开关速度会比 Q1 慢,关断时承受更高电压。

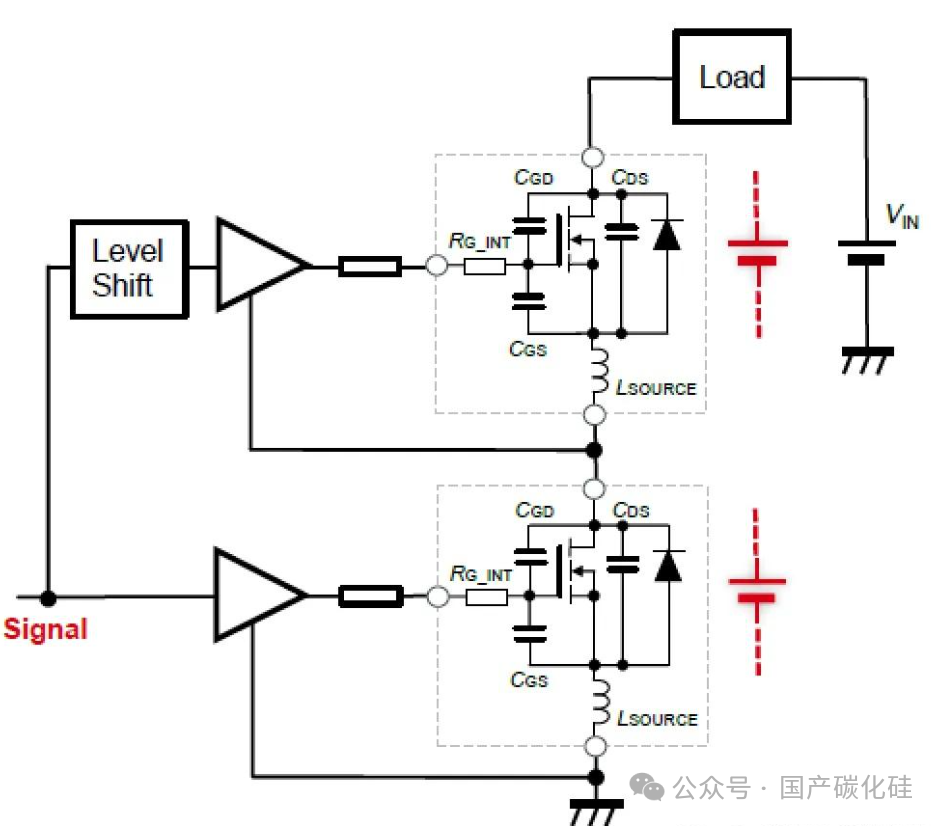

(2)驱动电路差异

驱动电路是栅极信号的 “传输通道”,任何环节的偏差都会影响开关同步性:

外接栅阻(RG_EXT)

RG_EXT 与 RG_INT 串联,直接决定栅极充电电流大小。RG_EXT 越大,充电电流越小,开关速度越慢。若 Q1 的 RG_EXT=1Ω,Q2 的 RG_EXT=1.5Ω,Q2 的开关速度会显著慢于 Q1,关断时电压集中在 Q2 上。 寄生电感与传输延迟

驱动信号线路的寄生电感(如布线电感)会延迟信号传输,若 Q1 与 Q2 的驱动线路长度不同,信号到达时间会有差异,导致开关不同步。

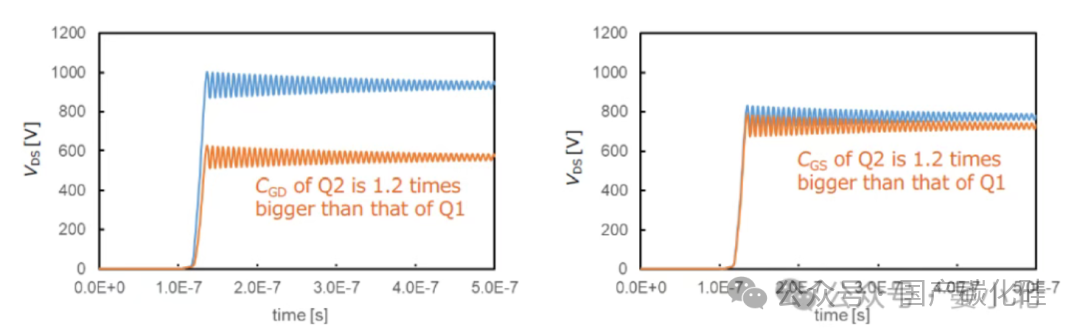

(3)寄生电容的 “差异化影响”:为什么 CGD 比 CGS 更关键?

仿真数据显示:当 Q2 的 CGD、CGS 分别为 Q1 的 1.2 倍时,CGD 偏差导致的分压不均程度,是 CGS 偏差的 3 倍以上。核心原因与栅极充电的两个阶段有关:

第一阶段(CGS 主导)

驱动电压开始上升,电流主要给 CGS 充电,VGS 从 0 上升到 Vth,此时 VDS 基本不变,分压无明显差异; 第二阶段(CGD 主导,米勒平台期)

VGS 达到 Vth 后,电流开始同时给 CGS 和 CGD 充电,VGS 进入 “平台期”,而 VDS 开始快速下降(开通)或上升(关断)。这一阶段是 VDS 变化最剧烈的时期,也是串联器件 “争夺分压” 的关键阶段 ——CGD 越大,栅极充电越慢,VDS 变化越滞后,自然会承受更高电压。

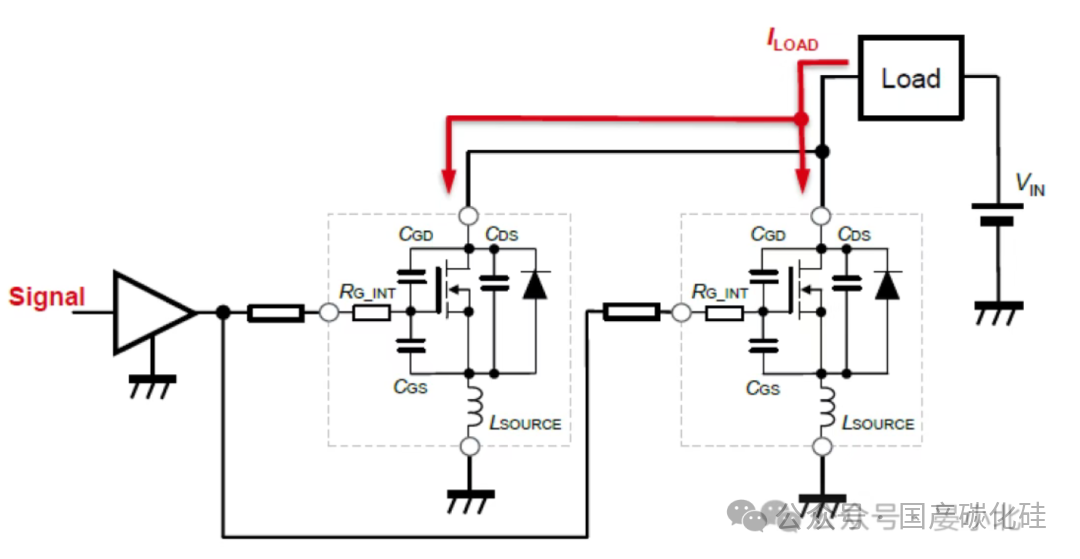

3 并联场景:分流不均与 VGS 振荡的 “双重挑战”

SiC MOSFET 并联的核心目标是分流—— 当负载电流(ILOAD)超过单个器件的额定漏极电流(ID 额定)时,通过 n 个器件并联,理论上每个器件仅承担 ILOAD/n 的电流。但实际应用中,动态分流不均与 VGS 振荡会成为两大核心隐患。

1. 静态均流 vs 动态不均:温度系数的 “双刃剑”

并联场景下,电流分布存在 “静态均衡、动态失衡” 的特点:

静态阶段(稳定导通)

电流会自发均衡,核心依赖导通电阻(Rdon)的正温度系数。若 Q1 的电流略大,其结温会升高,Rdon 随温度上升而增大(SiC MOSFET 的 Rdon 温度系数约为 0.004/℃),根据欧姆定律(I=V/R),Rdon 增大后,Q1 的电流会减小,最终实现电流均衡。 动态阶段(开通 / 关断)

电流严重不均,且开关速度快的器件会承受更高峰值电流。开通时,开关快的器件先达到导通状态,会 “抢” 走更多电流;关断时,开关快的器件先截止,电流会转移到未截止的器件上,导致其电流峰值升高。

仿真验证:当 Q1 与 Q2 存在 1V 的 Vth 偏差(Q2 的 Vth 低 1V)、0.5Ω 的 RG_EXT 偏差(RG1=1Ω,RG2=1.5Ω)时,Q2 的开通时间比 Q1 短 30%,峰值电流比 Q1 高 40%;若源极电感(LSOURCE)存在 2nH 的差异(Q1 的 LSOURCE=1nH,Q2 的 LSOURCE=3nH),Q2 的电流峰值会比 Q1 高 25% 以上。

2. 分流不均的 4 大关键因素

与串联场景相比,并联时的电流不均受更多因素影响,除了 Vth、寄生电容、驱动电路差异外,散热条件也成为关键变量:

Vth 偏差

Vth 低的器件先开通、后关断,始终处于 “提前导通、滞后关断” 的状态,自然会承担更多电流; 寄生元件与栅阻

CGD、CGS 的差异影响栅极充放电速度,RG_INT 与 RG_EXT 的差异影响充电电流,共同导致开关速度不同; 源极电感(LSOURCE)

源极电感会产生感应电动势(V=L×di/dt),若 Q1 与 Q2 的 LSOURCE 不同,感应电动势差异会改变栅源电压(VGS=V 驱动 - V 感应),进而影响漏极电流(ID)。仿真显示,仅 2nH 的 LSOURCE 偏差,就能导致 ID 差异超过 20%; 散热条件

若 Q1 的散热片接触不良,其结温会比 Q2 高,虽然静态时 Rdon 增大可均衡电流,但动态时高温会加速栅极氧化层老化,进一步扩大 Vth 偏差,形成 “温度升高→参数偏差扩大→电流更不均” 的恶性循环。

3. 隐藏风险:VGS 振荡的产生机制与危害

并联场景中,VGS 振荡是容易被忽视的 “隐形杀手”,一旦发生会导致栅极电压波动,甚至超过栅极额定电压(通常为 ±20V),损坏栅极氧化层。其产生机制可拆解为 3 步:

(1)寄生 RLC 谐振电路的形成

器件与驱动电路的寄生元件会构成天然的 RLC 谐振电路:

电阻(R)

包括器件内部栅阻(RG_INT)与外接栅阻(RG_EXT); 电感(L)

主要是驱动线路的布线电感(LTRACE)与源极电感(LSOURCE); 电容(C)

器件的寄生电容 CGD 或 CGS。

(2)电流不均注入振荡能量

理想状态下,若两个器件参数完全一致、驱动电路绝对对称,Q1 与 Q2 的栅压(VGS)时刻相等,器件间无能量交换,谐振电路不会被激活。但实际中,参数偏差导致电流不均,会向 RLC 电路注入能量 —— 例如 Q1 的电流比 Q2 大,LSOURCE 产生的感应电动势差异会在 Q1 与 Q2 的 GS/GD 间形成电势差,这个电势差就是振荡的 “初始能量”。

(3)高速开关加剧振荡

外接栅阻(RG_EXT)越小,栅极充电电流越大,开关速度越快,但同时也会降低 RLC 电路的阻尼系数(阻尼系数与 R 成正比)。阻尼系数越小,电路越容易发生谐振,VGS 振荡的幅度和持续时间会显著增加。因此,追求 “高速开关 + 大电流并联” 的场景(如新能源逆变器),VGS 振荡的风险会更高。

4 串并联核心控制策略与总结

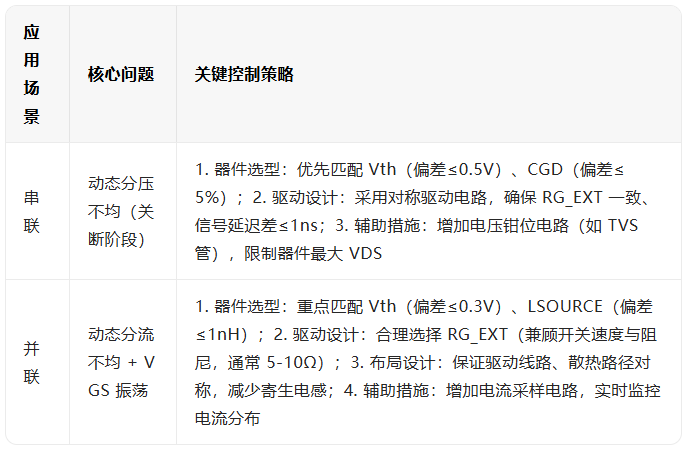

针对串并联场景的不同问题,需从 “参数匹配、驱动优化、布局设计” 三方面制定针对性方案,具体如下表所示:

最终总结

SiC MOSFET 串并联的本质,是 “通过多器件协同,突破单个器件的电压 / 电流限制”,但这一过程的前提是 “控制参数偏差”。串联的核心是 “解决关断阶段的电压分配问题”,需重点关注 CGD 与 Vth 的匹配;并联的核心是 “平衡动态电流与振荡风险”,需兼顾参数一致性、驱动对称性与布局合理性。

忽略这些细节,即使选用高性能 SiC MOSFET,也可能出现 “器件提前损坏、电路可靠性下降” 的问题。因此,在实际设计中,需从选型、驱动、布局全流程控制偏差,才能充分发挥 SiC MOSFET 的高频、高效优势。

国产碳化硅,就找明古微--感谢深圳市明古微半导体有限公司长期对本公众号的赞助与支持,深圳市明古微半导体有限公司作为爱仕特科技碳化硅MOS/SBD、中科本原DSP、乐山希尔整流桥堆/FRD等的核心代理商,与其深度合作并联合开发功率模块及电驱、储能系统,为电动汽车、OBC、DC-DC、充电桩、光伏逆变、SVG、PCS、工业电源、家电变频等能源产业提供完整解决方案,更多信息请登录:wwwmgmsemi.com

SiC MOS

更多信息请关注

微信公众号

邮箱:ymq@mgmsemi.com

深圳:深圳市光明区光明街道华强科技生态园5A栋1216

成都:成都市高新区双柏路68号汇创天下科技园西区1栋9层907

长沙:长沙市岳麓区麓谷科技创新创业园A1栋2404

上海:上海市闵行区万源路2161弄150号1号楼318

菲律宾:12 Ibayo St, Manila, Metro Manila, Philippines