明古微半导体

MGME SEMICONDUCTOR

碳化硅功率器件+电驱方案

新能源汽车.充电桩.工业电源.光伏储能.电力电子.低空飞行器...

国产碳化硅 就找明古微

技术学院

STUDY

在碳化硅功率器件的版图里,有一个绕不开的话题:为何 NMOS 能独当一面,而 PMOS 却始终 “查无此人”?这并非技术路线的偶然选择,而是材料特性与器件物理规律共同编织的 “先天困局”。本文将从材料本质出发,拆解碳化硅 PMOS 的技术瓶颈,探讨潜在突破方向,并解析行业如何在 “无 PMOS” 的前提下构建高效电路。

1 材料基因:空穴的 “先天缺陷” 决定性能天花板

碳化硅 PMOS 的核心困境,源于 P 型半导体中载流子 ——空穴的 “先天不足”。

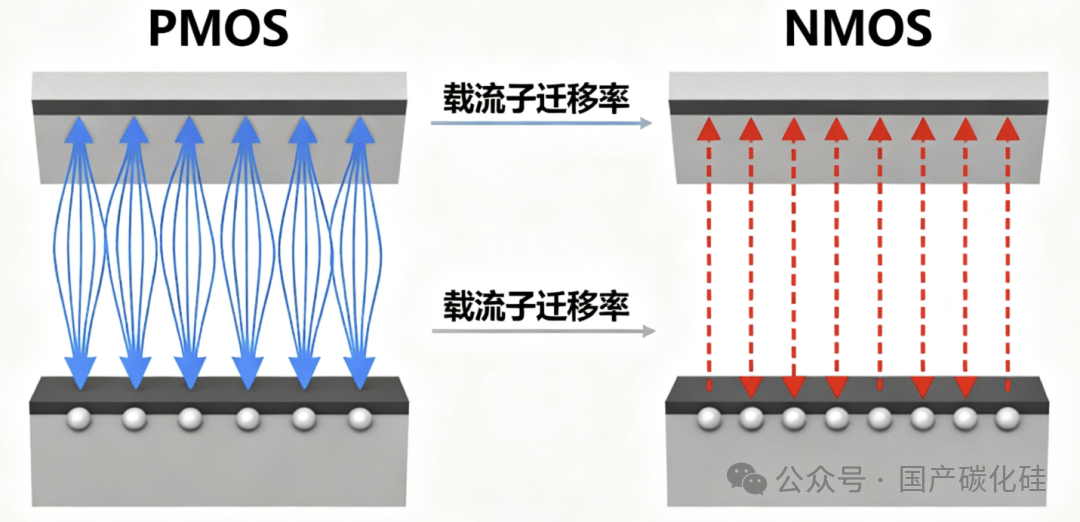

在半导体中,载流子迁移率直接决定器件的导通能力与开关速度。碳化硅的电子迁移率(N 型)可达 900-1200 cm²/(V・s),而空穴迁移率(P 型)仅为 100-200 cm²/(V・s),差距高达 5-10 倍。这种悬殊在器件层面会引发连锁反应:

导通电阻飙升

相同尺寸下,PMOS 的导通电阻(Rₒₙ)是 NMOS 的 5-10 倍,导致功耗激增。以 650V 器件为例,NMOS 的 Rₒₙ・A(导通电阻与面积乘积)可低至 5 mΩ・cm²,而 PMOS 往往超过 30 mΩ・cm²,失去碳化硅 “高效” 的核心优势。 开关速度滞后

空穴迁移率低导致沟道载流子响应缓慢,开关损耗(Eₒₙ/Eₒff)比 NMOS 高 3-5 倍,难以满足高频应用需求。 温度特性恶化

空穴迁移率随温度升高下降更快(温度系数更负),高温下 PMOS 性能衰减比 NMOS 更严重,可靠性风险陡增。

更深层的原因在于碳化硅的晶体结构。4H-SiC(主流商用晶型)的导带底由多个等价能谷组成,电子可通过谷间散射实现高迁移率;而价带结构复杂,轻空穴与重空穴的有效质量差异大,散射概率高,导致空穴迁移率被 “锁死” 在低水平。这种材料本征特性,成为 PMOS 难以逾越的第一道鸿沟。

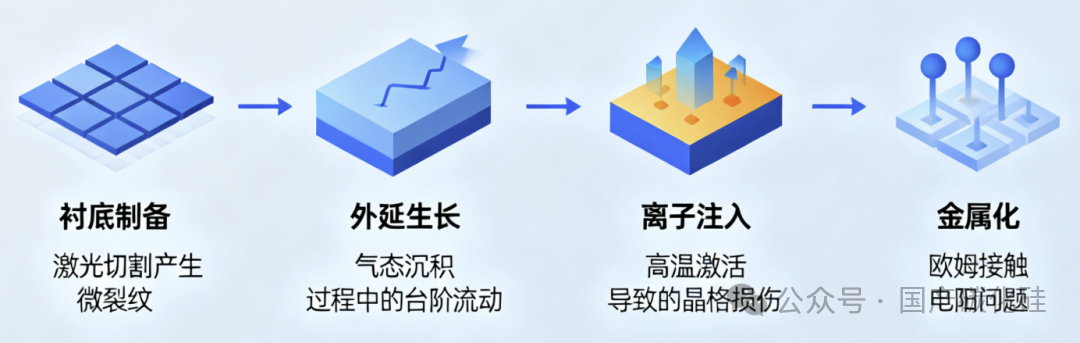

2 工艺瓶颈:从界面到阈值的 “后天难题”

即便克服了材料本征限制,碳化硅 PMOS 的工艺实现仍面临多重挑战:

栅氧界面缺陷密集碳化硅与二氧化硅(SiO₂)的界面缺陷密度(Dₒₜ)是影响载流子迁移率的关键。P 型碳化硅(尤其是 Al 掺杂)与 SiO₂的界面存在更多碳悬键和氧空位,Dₒₜ可达 10¹³ cm⁻²・eV⁻¹,是 N 型界面的 2-3 倍。这些缺陷会捕获空穴,进一步降低沟道迁移率,同时导致阈值电压漂移(ΔVₜₕ)。

阈值电压控制困难PMOS 的阈值电压(Vₜₕ)绝对值通常仅为 - 2V 至 - 4V,远低于 NMOS 的 3-5V,且受工艺波动(如掺杂浓度、栅氧厚度)影响更大。在高压应用中,低绝对值 Vₜₕ易导致器件 “误开通”,必须通过复杂的栅极驱动保护电路弥补,增加系统成本。

体二极管性能劣化碳化硅 PMOS 的体内寄生二极管(由 P 型衬底与 N 型漂移区形成)反向恢复电荷(Qᵣᵣ)远高于 NMOS,且正向导通电压(Vբ)更大,在续流场景下功耗激增,失去碳化硅器件 “高频软开关” 的优势。

3 PMOS 的 “理想应用场景”:哪些地方其实需要它?

尽管性能受限,PMOS 在电路拓扑中仍有不可替代的潜在价值:

互补对称电路(CMOS)在低压小功率场景(如 100V 以下),CMOS 结构可通过 NMOS 与 PMOS 的互补导通实现低功耗逻辑控制。例如,碳化硅 CMOS 驱动芯片能与功率器件单片集成,减少寄生参数,但 PMOS 的低性能使其难以突破 100V 电压等级。

同步整流与双向开关在新能源汽车 OBC(车载充电机)、储能变流器等需要双向电流控制的场景,PMOS 与 NMOS 组成的同步整流桥可降低反向导通损耗。若没有 PMOS,需采用更复杂的图腾柱结构或牺牲效率换取兼容性。

高压电平转换在高压隔离驱动电路中,PMOS 可作为高端开关管实现电平抬升,简化自举电路设计。但现有方案中,这一功能往往由耐高压 NMOS 配合电荷泵替代,增加了驱动电路的复杂度。

4 无 PMOS 时代:行业如何 “曲线救国”?

既然 PMOS 难以实用化,行业已发展出成熟的替代方案,在 “全 N 型” 路线上实现高效电路设计:

图腾柱拓扑:用 NMOS 模拟互补功能在逆变器、整流器等需要上下管互补导通的场景,采用两个 NMOS 堆叠(上管为高压 NMOS,下管为低压 NMOS),通过自举电路(Bootstrap)为上管栅极提供高于源极的驱动电压,模拟 PMOS 的 “拉低” 功能。例如,光伏逆变器中采用的图腾柱 PFC 电路,仅用 NMOS 即可实现功率因数校正,效率比传统二极管整流提升 2-3 个百分点。

电荷泵驱动:解决高压浮置问题对于需要高端开关的电路(如半桥拓扑),通过电荷泵将驱动电压抬升至母线电压以上,确保 NMOS 上管可靠导通。这种方案虽增加了驱动芯片的复杂度,但避免了 PMOS 的低效率问题,在新能源汽车电机控制器中已广泛应用。

多芯片并联:弥补单管性能不足若需更大电流,可通过多颗 NMOS 并联降低总导通电阻,替代 “单颗 PMOS + 单颗 NMOS” 的互补结构。例如,在 1200V/100A 的充电桩模块中,4 颗 25A NMOS 并联的总损耗(约 50W)仍低于 1 颗 100A PMOS(约 80W),且成本更低。

宽禁带混合方案:SiC NMOS+GaN HEMT在超高频场景(如 MHz 级电源),采用碳化硅 NMOS(高压侧)与氮化镓 HEMT(低压侧)组合,利用 GaN 的高频低阻特性弥补 PMOS 的缺失。这种混合拓扑在服务器电源中已实现效率突破 98%。

5 破局方向:PMOS 还有机会吗?

尽管挑战重重,学术界与企业仍在探索碳化硅 PMOS 的突破路径:

异质结界面优化用 Al₂O₃、HfO₂等高介电常数(高 k)材料替代 SiO₂作为栅介质,减少界面缺陷。实验数据显示,Al₂O₃栅 PMOS 的空穴迁移率可提升至 250 cm²/(V・s),较 SiO₂方案提升 25%,但长期可靠性仍需验证。

3D 结构设计采用垂直沟道或 FinFET 结构增加沟道宽度,降低导通电阻。美国北卡罗来纳州立大学的研究显示,4H-SiC FinFET PMOS 的 Rₒₙ・A 可降至 15 mΩ・cm²(650V),接近商用 NMOS 的水平,但工艺复杂度极高,量产成本难以控制。

新型掺杂技术采用氮(N)与铝(Al)共掺杂优化 P 型碳化硅的电学特性,或通过离子注入形成超浅结,减少空穴散射。英飞凌的实验表明,优化掺杂后的 PMOS 阈值电压稳定性提升 40%,但仍未达到商用标准。

结语:接受 “不完美”,在限制中寻找最优解

碳化硅 PMOS 的缺失,本质是材料物理规律对工程技术的约束。与其强行突破 “不可能”,不如在 “全 N 型” 路线上深耕优化 —— 这正是行业的现实选择。从图腾柱拓扑到混合宽禁带方案,工程师用创新绕过了材料的先天缺陷,让碳化硅在新能源、电动汽车等领域持续突破效率极限。

未来,随着异质结、3D 结构等技术的成熟,PMOS 或许能在特定场景(如低压 CMOS)找到立足之地,但在高压大功率领域,NMOS 的主导地位仍将长期存在。毕竟,半导体技术的进步,从来不是与物理规律对抗,而是在理解规律后,找到最适合的应用路径。

国产碳化硅,就找明古微--感谢深圳市明古微半导体有限公司长期对本公众号的赞助与支持,深圳市明古微半导体有限公司作为爱仕特科技碳化硅MOS/SBD、中科本原DSP、乐山希尔整流桥堆/FRD等的核心代理商,与其深度合作并联合开发功率模块及电驱、储能系统,为电动汽车、OBC、DC-DC、充电桩、光伏逆变、SVG、PCS、工业电源、家电变频等能源产业提供完整解决方案,更多信息请登录:wwwmgmsemi.com

SiC MOS

更多信息请关注

微信公众号

邮箱:ymq@mgmsemi.com

深圳:深圳市光明区光明街道华强科技生态园5A栋1216

成都:成都市高新区双柏路68号汇创天下科技园西区1栋9层907

长沙:长沙市岳麓区麓谷科技创新创业园A1栋2404

上海:上海市闵行区万源路2161弄150号1号楼318

菲律宾:12 Ibayo St, Manila, Metro Manila, Philippines