MOSFET和IGBT等电源开关元器件被广泛应用于各种电源应用和电源线路中。另外,所使用的电路方式也多种多样,除单独使用外,还有串联连接、并联连接等多种使用方法。其中,在将开关元件上下串联连接的桥式结构中,通常交替地导通与关断各个元器件。下面是常规的桥式结构同步方式boost电路,波形图是根据栅极信号交替地导通/关断的低边(LS)MOSFET和高边(HS)MOSFET的漏极-源极间电压(VDS)和漏极电流(ID)示例。

通过开关工作,流过各元件的电流和变化的电压以复杂的方式相互影响。尤其是在处理高电压高电流的电路中,受安装电路板和结线引起的寄生分量等影响,产生电压和电流的动作,并因此导致工作不稳定、效率下降,从而可能导致损耗增加、产生异常发热等问题。近年来,SiC MOSFET等高性能功率元器件的应用,使得通过高速开关转换大功率成为可能,但在操作过程中,需要对开关工作有深入的了解。在该系列文章中,我们将着眼于MOSFET桥式结构中的各MOSFET的栅极-源极间电压的动作,以简单的同步方式boost电路为例,对以下内容进行探讨:

SiC MOSFET的桥式结构

下面给出的电路图是在桥式结构中使用SiC MOSFET时最简单的同步式boost电路。该电路中使用的SiC MOSFET的高边(HS)和低边(LS)是交替导通的,为了防止HS和LS同时导通,设置了两个SiC MOSFET均为OFF的死区时间。右下方的波形表示其门极信号(VG)时序。

该电路中HS和LS MOSFET的Drain-Source电压(VDS)和漏极电流(ID)的波形示意图如下。这是电感L的电流处于连续动作状态,即所谓的硬开关状态的波形。

横轴表示时间,时间范围Tk(k=1~8)的定义如下:

· T1: LS为ON时、MOSFET电流变化的时间段

· T2: LS为ON时、MOSFET电压变化的时间段

· T3: LS为ON时的时间段

· T4: LS为OFF时、MOSFET电压变化的时间段

· T5: LS为OFF时、MOSFET电流变化的时间段

· T4~T6: HS变为ON之前的死区时间

· T7: HS为ON的时间段(同步整流时间段)

· T8: HS为OFF时、LS变为ON之前的死区时间

SiC MOSFET桥式结构的栅极驱动电路

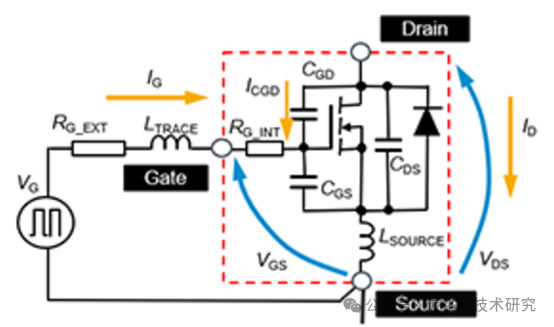

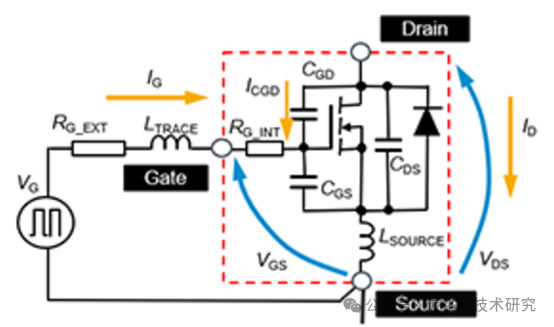

LS(低边)侧SiC MOSFET Turn-on和Turn-off时的VDS和ID的变化方式不同。在探讨SiC MOSFET的这种变化对Gate-Source电压(VGS)带来的影响时,需要在包括SiC MOSFET的栅极驱动电路的寄生分量在内的等效电路基础上进行考量。下图是最基本的栅极驱动电路和SiC MOSFET的等效电路。栅极驱动电路中包括栅极信号(VG)、SiC MOSFET内部的栅极线路内阻(RG_INT)、以及SiC MOSFET的封装的源极电感量(LSOURCE)、栅极电路局部产生的电感量(LTRACE)和外加栅极电阻(RG_INT)。

关于各电压和电流的极性,需要在等效电路图中,以栅极电流(IG)和漏极电流(ID)所示的方向为正,以源极引脚为基准来定义VGS和VDS。SiC MOSFET内部的栅极线路中也存在电感量,但由于它比LTRACE小,因此在此忽略不计。

导通(Turn-on)/关断( Turn-off)动作

为了理解桥式电路的Turn-on / Turn-off动作,下面对前文中提到的桥式电路中各SiC MOSFET的电压和电流波形进行详细说明。下面的波形图与上次的波形图是相同的。我们和前面的等效电路图结合起来进行说明。当正的VG被施加给LS侧栅极信号以使LS侧ON时,Gate-Source间电容(CGS)开始充电,VGS上升,当达到SiC MOSFET的栅极阈值电压(VGS(th))以上时, LS的ID开始流动,同时从源极流向漏极方向的HS侧ID开始减少。这个时间范围就是前文中定义的T1(见波形图最下方)。接下来,当HS侧的ID变为零、寄生二极管 Turn-off时,与中间点的电压(VSW)开始下降的同时,将对HS侧的Drain-Source间电容(CDS)及Drain-Gate间电容(CGD)进行充电(波形图T2)。对该HS侧的CDS+CGD充电(LS侧放电)完成后,当LS侧的VGS达到指定的电压值,LS侧的 Turn-on动作完成。而Turn-off动作则在LS侧VGOFF时开始,LS侧的CGS蓄积的电荷开始放电,当达到SiC MOSFET的平台电压(进入米勒效应区)时,LS侧的VDS开始上升,同时VSW上升。在这个时间点,大部分负载电流仍在LS侧流动(波形图T4),HS侧的寄生二极管还没有转流电流。LS侧的CDS+CGD充电(HS侧为放电)完成时,VSW超过输入电压(E),HS侧的寄生二极管Turn-on,LS侧的ID开始转向HS侧流动(波形图T5)。LS侧的ID最终变为零,进入死区时间(波形图T6),当正的VG被加给HS侧MOSFET的栅极信号时Turn-on,进入同步工作时间(波形图T7)。

桥式电路的开关产生的电流和电压

在前文中对SiC MOSFET桥式结构的栅极驱动电路的导通(Turn-on)/关断( Turn-off)动作进行了解说。接下来将介绍在SiC MOSFET这一系列开关动作中,SiC MOSFET的VDS和ID的变化会产生什么样的电流和电压。下面的电路图是SiC MOSFET桥式结构的同步式boost电路,LS开关导通时的示例。电路图中包括SiC MOSFET的寄生电容、电感、电阻,HS和LS的SiC MOSFET的VDS和ID的变化带来的各处的栅极电流(绿色线)。

ID的变化dID/dt所产生的电压

ID的变化将会产生下述公式(1)所示的电压。

这是由于存在于SiC MOSFET源极的寄生电感中流过ID而产生的电压,是由电路图中的(I)引起的。该电压会使电流(I’)流过。以HS为例,当SiC MOSFET关断、VDS变化时,Gate-Drain寄生电容CGD中会流过电流ICGD。如电路图所示,该电流分为Gate-Source寄生电容CGS侧流过的电流ICGD1:(II)-1和栅极电路侧流过的电流ICGD2:(II)-2。当VDS开始变化时,栅极电路侧的阻抗较大,因此大部分ICGD都在CGS侧,此时的ICGD1如公式(2)所示。

从公式可以看出,当CGD较大时或CGD/CGS的比值变小时,ICGD1会增加。dVDS/dt和dID/dt既可以为正也可以为负,所以因它们而产生的电流和电压的极性在导通(Turn-on)和关断(Turn-off)时是不同的。

SiC MOSFET低边开关导通时的Gate-Source间电压的动作

当SiC MOSFET的LS导通时,首先ID会变化(下述波形示意图T1)。此时LS的ID沿增加方向、HS的ID沿减少方向流动,受下述等效电路图中所示的事件(I)影响,在图中所示的极性产生公式(1)的电动势。公式(1)与上一篇文章中使用的公式相同。该电动势引起的电流将源极侧作为正极对CGS进行充电,因此在LS会将VGS向下推,在HS会将VGS向负极侧拉,使之产生负浪涌(波形示意图VGS的T1)。

当ID的变化结束时,LS的VDS的电位降低(波形示意图T2)。所以,公式(2)中的电流就像等效电路图中的(II)-1、(II)-2那样流动,并且VGS会分别引发下列公式(3)、(4)中的电压上升。

VDS刚刚开始变化后,公式(3)的VGS上升为主,随着时间的推移,公式(4)的VGS也开始上升。也就是说,MOSFET的CGD/CGS比、驱动电路的RG_EXT、栅极驱动信号图形布线的电感值LTRACE具有很大影响。如等效电路图所示,HS中的(II)-2的电流ICGD2处于VGS提升方向。因此,本来应该处于OFF状态的HS因VGS的提升而开始了导通工作。这种现象称为“误启动”。当HS发生误启动时,就会与LS的导通工作重叠,致使HS和LS的MOSFET同时导通,从而引发直通电流。ICGD2会持续流动到LS的导通工作结束,并被积蓄在LTRACE中,但会在VSW变化结束的时间点消失,LTRACE产生电动势。这就是事件(III)。受RG_EXT等开关条件影响,ICGD2可能会达到几安培,并且该电动势可能会增加。受上述事件(I)、(II)、(III)的影响,LS导通后的Gate-Source电压呈现出波形示意图中所示的动作。波形示意图和等效电路图的相同编号表示同一事件。另外,图中VGS的虚线波形表示理想的波形。

外置栅极电阻的影响

下面是SiC MOSFET桥式结构的LS导通时的双脉冲测试结果。(a)波形图的外置栅极电阻RG_EXT为0Ω,(b)为10Ω。图中的(I)、(II)、(III)同前面相应编号的事件。

比较(a)和(b)的波形可以看出,RG_EXT越小,由事件(I)引起的VGS下降就越大。此外,由于开关速度非常快,因此事件(III)在(a)中很突出;但由于RG_EXT为0Ω,因此几乎没有观察到事件(II)的波形。另一方面,在(b)中,事件(II)-2和RG_EXT引起的VGS升程明显。从该结果可以清楚地看出,要想降低诱发LS导通时HS误启动的事件(II)-2的VGS升程,就需要减小HS关断时的外置栅极电阻RG_EXT。然而,多数情况下,HS和LS的RG_EXT是相同的,因此,当减小RG_EXT时,LS的dVDS/dt将增加,如公式(1)所示,HS的ICGD会增加。从公式(4)可以看出,结果会导致HS浪涌升高。有一种对策方法是,使导通时和关断时的RG_EXT分离,并且仅减小关断时的RG_EXT。常规方法是使用二极管的方法,如右图所示。使用这种方法,在导通状态下工作的电阻只有RG_ON,而在关断状态下,二极管导通并成为RG_ON和RG_OFF的并联电阻。因此,相对于导通时的电阻值,关断时的电阻值变小。

另外,与最前面说明中使用的波形示意图不同,HS的VGS波形之所以在紧靠事件(I)之前的位置向正极侧振荡,是因为事件(I)的电流开始流动的瞬间LSOURCE引起的电动势在通过CGS后立即被观测到了。

低边开关关断时的栅极 – 源极间电压的动作

下面是表示LS MOSFET关断时的电流动作的等效电路和波形示意图。与导通时的做法一样,为各事件进行了(IV)、(V)、(VI)编号。与导通时相比,只是VDS和ID变化的顺序发生了改变,其他基本动作是一样的。与导通时的事件之间的对应关系如下:

关断 |

| 导通 |

事件(IV) | → | 事件(II) |

事件(V) | → | 事件(III) |

事件(VI) | → | 事件(I) |

dVDS/dt带来的LS的VGS上升和HS的VGS负浪涌(波形示意图T4)是事件(IV)。

波形示意图的T4周期结束时,公式(1)所示的ICGD1消失时发生的浪涌是事件(V)。公式(1)与之前使用的公式相同。然后,漏极电流发生变化(波形示意图T6),并发生公式(2)所示的LSOURCE引起的电动势,电流如等效电路的事件(VI)中所示流动。公式(2)也与之前使用的公式相同。

可以看出的动作是,由于该电流以源极侧为负极向MOSFET的CGS充电,因此在HS侧将VGS推高,在LS侧将VGS向正极侧拉升,以防止VGS下降。结果就产生了波形示意图所示的VGS动作。波形示意图中VGS的虚线表示理想的电压波形。

外置栅极电阻的影响

下面是SiC MOSFET桥式结构的LS关断时的双脉冲测试结果。(a)波形图的外置栅极电阻RG_EXT为0Ω时,(b)为10Ω。图中的(IV)、(V)、(VI)即前面提到的事件。

如波形图所示,可以看到事件(V)的浪涌非常明显。

尽管由VDS的变化引起的事件(IV)的影响很小,但由于HS中事件(IV)引起的负浪涌常常会超过额定值,在这种情况下,就需要对电路采取相应的措施。要想减少这种关断时的HS负浪涌,需要减小HS栅极电阻RG_EXT。然而,需要注意的是,在前面介绍过的常用栅极电阻调节电路中,事件(IV)在电阻值高的RG_ON侧较为突出。关于由事件(VI)引起的VGS抬升,由于该时刻正好在关断(Turn-off)结束之前,所以即使HS进入导通(Turn-on)动作,SiC MOSFET桥式结构的LS也已经被关断,几乎不会造成什么问题。由于SiC MOSFET的动作相互之间没有关联,因此桥式结构中SiC MOSFET的栅极电压非常复杂。此外,栅极驱动电路的条件不同其动作也有显著差异。

例如,即使电路方式、所使用的SiC MOSFET以及其他部件相同,也可能因仅仅更改了电路板或布线布局而表现出完全不同的动作。也可以说应该重点关注“动作因电路板和布线的不同而显著不同”这点,在电路板或布局不同的情况下,如果因为电路具有良好的记录而忽略了评估,将会造成严重的后果。了解了这里提到的基本工作和波形动作机制,将有助于处理在实际设计过程中遇到的问题。这次使用的示例是一个对LS SiC MOSFET进行开关的升压电路,不过在对HS SiC MOSFET进行开关的降压电路中,仅仅是LS和HS的替换,动作是相同的。因此,可以作为使用硬开关的各种电路拓扑中的基本思想来应用。

声明:此文部分内容取自网络素材,文中观点仅供分享交流,仅为传递信息为目的,若有来源标注错误或如涉及版权等问题,请与作者联系,将及时更正、删除,谢谢。