明古微半导体

MGME SEMICONDUCTOR

碳化硅功率器件+电驱方案

新能源汽车.充电桩.工业电源.光伏储能.电力电子.低空飞行器...

国产碳化硅 就找明古微

技术学院

STUDY

关于碳化硅MOS并联使用,特别是驱动部分的处理,需要格外谨慎。SiC MOS的高开关速度使得并联时的动态均流挑战更大。通常在设计中,工程师们更愿意使用同一个驱动信号源,经过两路完全独立、匹配的驱动器(栅极驱动芯片)分别驱动两颗并联的MOS。这就要关注并联的两颗MOS阈值,Rdson等参数是否具有一致性。这对于碳化硅MOS供应商是有很大的挑战。

以下是并联使用碳化硅MOS的关键注意事项,重点关注驱动部分:其核心挑战在于实现动态均流。

1、驱动信号的严格同步与匹配

为了确保并联的每个器件在完全相同的时刻开通和关断,避免因开关时间不同步导致一个器件承受更大的电流应力(开通时先导通的管承受全部di/dt,关断时后关断的管承受全部电流)。因此在设计时就需要有独立的栅极驱动通道,常用的方案:同一个PWM控制信号源,两个完全独立且匹配的栅极驱动芯片分别驱动两个MOS。 这是实现良好同步和匹配的基础。另外在器件选型时一定要注意选择同一批次、规格书明确标注传播延迟匹配度高的栅极驱动芯片(例如,匹配度在几纳秒以内)。仔细比较不同驱动芯片的数据手册。

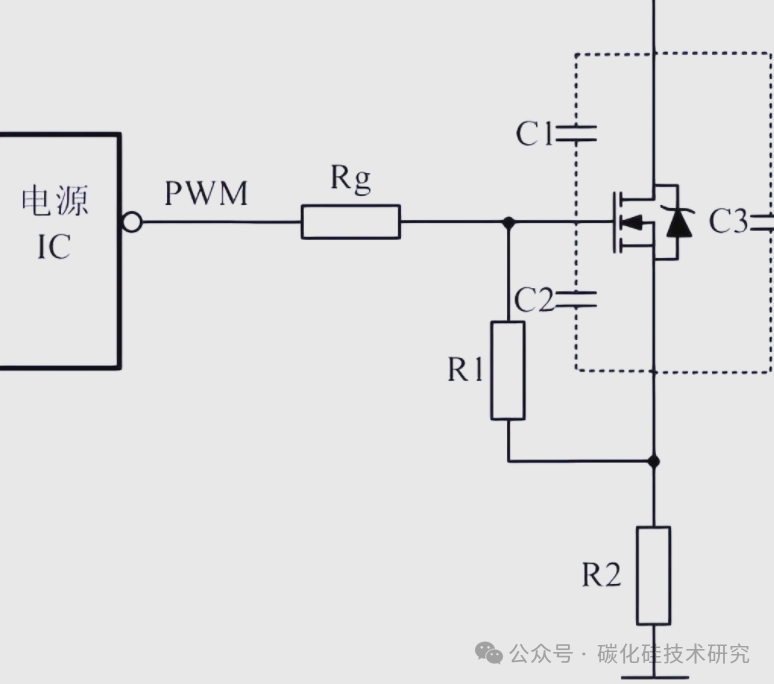

驱动回路布局方面需要用对称方式:从驱动芯片输出到MOS栅极的PCB走线长度、宽度、层叠结构必须完全相同。等长布线至关重要。以减小寄生电感差异。驱动芯片的电源退耦电容(靠近驱动芯片VCC和GND引脚)也需要对称布置。另外还需要独立的栅极电阻。即: 为每个MOS配备独立的、阻值经过精确匹配的栅极电阻(Rg_on, Rg_off)。这样处理之后,即使器件参数和布局有微小差异,也可以通过微调Rg来补偿开关速度,优化均流。

采用独立电阻有助于抑制栅极回路和功率回路耦合引起的振荡。Rg值需要根据具体器件、布局和开关速度要求优化选择(通常在几欧姆到几十欧姆)。

2、源极电感的匹配与最小化:

MOS的开关行为(尤其是开通)由其栅源电压Vgs决定。源极引线或PCB走线上的寄生电感(Lsource)会在开关瞬态产生感应电压(V = L * di/dt),这个电压会抵消实际作用在器件内部的Vgs。如果并联器件的寄生电感不同,即使驱动芯片输出的Vgs相同,作用在器件内部的有效Vgs也会不同,导致开关速度不同,进而破坏动态均流。寄生电感的差异是动态不均流的主要原因之一。通常我们会采取以下方式解决:

开尔文源极连接: 这是至关重要的!每个MOS必须使用独立的开尔文源极(Kelvin Source)引脚(如果有)或专门的、低感抗的源极电流检测点,将其直接、独立、对称地连接到对应的驱动芯片的源极参考地(PGND或SOUTH引脚)。

功率源极连接对称: 连接到主功率回路(直流母线电容负极)的源极引脚(Power Source)的PCB走线也要尽量对称且低感抗。

最小化回路面积: 驱动回路(栅极-开尔文源极)和功率回路(漏极-功率源极)的面积都要最小化。

3、驱动部分和功率部分隔离

首先我们需要足够的驱动能力来确保每个栅极驱动芯片能为对应MOS的栅极电荷(Qg)提供足够的峰值电流(Ipeak = Vdrv / Rg, Vdrv通常15V或18V),以维持所需的开关速度。SiC MOS的Qg通常比同规格Si MOS小,但开关频率可能更高。

如果并联的MOS位于不同的电位(例如半桥拓扑的上管),则每个驱动通道都需要独立的隔离电源和隔离信号传输(如光耦、数字隔离器、变压器驱动)。

除了驱动部分,并联还需注意的其他关键点?

1、器件选配:

导通电阻Rds(on)匹配: 尽量选择同一批次、导通电阻(Rds(on))接近的器件,以改善稳态(导通状态)均流。虽然驱动匹配对动态均流更重要,但Rds(on)匹配有助于整体损耗均衡。

阈值电压匹配: Vgs(th)的匹配对开通时刻的一致性有一定影响,选择Vgs(th)接近的器件更好。

跨导匹配: 跨导(gfs)影响开通速度,也应尽量匹配。

2、PCB布局对称性:

功率回路对称: 直流母线电容 -> MOS漏极 -> MOS源极 -> 母线电容负极的功率回路布局必须高度对称。这意味着并联器件的漏极、源极(功率源极)到主电容的走线长度、宽度、层叠、过孔数量应完全相同。使用多层板,利用内层铺铜降低电感。

热对称: 确保两个器件在散热器上的安装位置对称,热阻一致,避免因温度不均导致Rds(on)漂移不同而影响稳态均流。

3、热设计与散热:

即使均流良好,并联器件也会产生热量。必须配备足够尺寸和性能的散热器,确保结温在安全范围内。良好的热对称性是基础。

4、电流检测与保护:

最好能为每个并联支路设置独立的电流检测(如分流电阻、电流传感器),以便精确监控每个器件的电流,实现更精细的保护(过流、短路)和均流状态诊断。如果只能检测总电流,保护阈值需要根据并联数量设定,但无法定位哪个器件失效或过流。

5、缓冲电路:

在极高di/dt或dv/dt应用或布局难以做到完美对称时,可以考虑在漏极或漏-源间增加小容量、低感抗的RC缓冲电路,帮助抑制电压尖峰和振荡,提高可靠性。但需仔细设计,避免增加过多损耗。

经常有人问到能否用同一个驱动经过两路独立驱动器分别驱动两颗SiC MOS。答案是肯定的。并且这是实现并联SiC MOS动态均流的最佳实践方案之一。这个在前文中我们的提到过。下面就简单描述一下:

方案: 你的控制器(MCU, PWM IC)产生一个PWM信号。这个信号同时(通过匹配的走线)输入到两个完全相同的、独立工作的栅极驱动芯片的输入端。每个栅极驱动芯片都有自己的电源、自己的输出级、自己的栅极电阻(Rg_on, Rg_off)、自己的开尔文源极连接回路,独立地驱动一个MOS。

具有的优势:

1、电气隔离: 驱动芯片本身通常能提供所需的电气隔离(如果使用隔离型驱动芯片)。

2、驱动能力: 专用驱动芯片提供足够的峰值电流驱动栅极。

3、匹配性: 使用同一型号、同一批次的驱动芯片,其传播延迟、上升/下降时间特性天然匹配度较高。

4、独立可调: 每个通道的栅极电阻可以独立选择和优化,用于微调开关速度和抑制振荡。

5、开尔文连接: 每个驱动通道都能独立实现到其对应MOS开尔文源极的低感抗连接,这是解决源极电感不匹配问题的关键。

6、布局对称性更容易实现: 相对于用一个驱动芯片驱动两个栅极(需要分叉走线),两个独立驱动的布局更容易做到从驱动芯片输出到MOS栅极/源极的完全对称。

特别注意:两个驱动芯片必须是同型号、同批次。

务必在设计阶段投入大量精力进行细致的布局规划,并在原型阶段使用示波器仔细测量每个器件的Vgs、Vds和电流波形,验证动态均流效果,并根据实测结果优化栅极电阻值和布局细节。在SiC MOS并联应用中,布局和驱动的对称性要求远高于传统的硅IGBT或MOS。 成功的并联能有效提升功率能力,但设计不当极易导致个别器件过应力失效。

SiC MOS

更多信息请关注

微信公众号

邮箱:ymq@mgmsemi.com

深圳:深圳市光明区光明街道华强科技生态园5A栋1216

成都:成都市高新区双柏路68号汇创天下科技园西区1栋9层907

长沙:长沙市岳麓区麓谷科技创新创业园A1栋2404

上海:上海市闵行区万源路2161弄150号1号楼318

菲律宾:12 Ibayo St, Manila, Metro Manila, Philippines