明古微半导体

MGME SEMICONDUCTOR

碳化硅功率器件+电驱方案

新能源汽车.充电桩.工业电源.光伏储能.电力电子.低空飞行器...

国产碳化硅 就找明古微

技术学院

STUDY

IGBT(硅基绝缘栅双极晶体管)和SiC MOSFET(碳化硅金属氧化物半导体场效应晶体管)在关断驱动策略上的差异,根源在于它们结构、工作原理和材料特性的本质不同。让我们透过现象看本质:

核心原因剖析

1. 阈值电压稳定性与抗干扰能力:

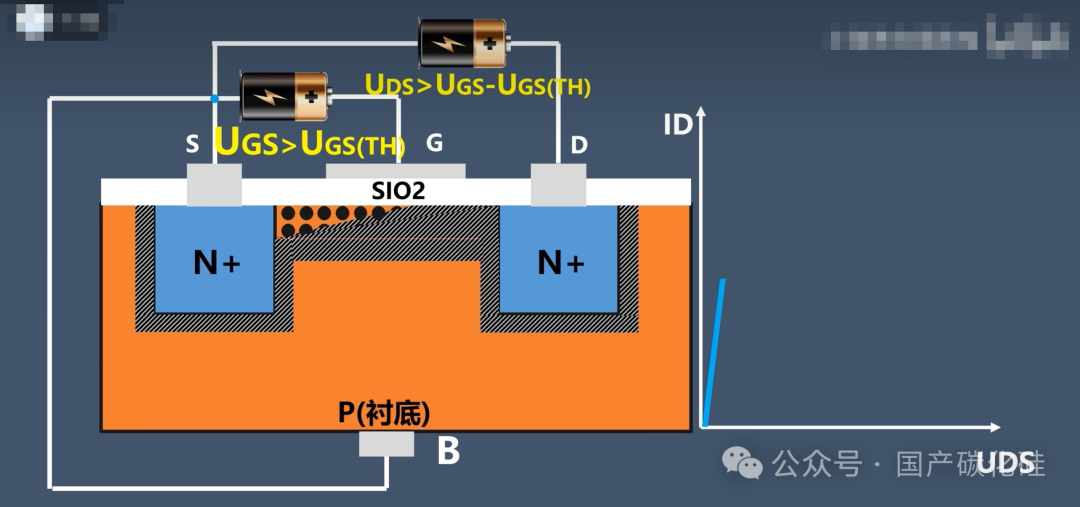

IGBT: 其本质是一个少数载流子器件(空穴注入N-漂移区),栅极控制的是MOS沟道(电子),但主电流路径是双极性的。栅极阈值电压(Vth)相对较高(通常在5-7V)且比较稳定。即使关断过程中漏极电压快速上升(dV/dt)通过米勒电容(Cgd)耦合到栅极产生一个“米勒平台”(通常在10-15V),这个平台电压远高于器件的阈值电压。因此,即使栅极驱动在0V,这个耦合电压不足以使栅极电压达到或超过阈值电压,从而不会导致器件意外开通(误导通)。

SiC MOSFET: 是多数载流子器件,其工作原理完全依赖于MOS沟道。SiC MOSFET的栅极阈值电压(Vth)通常较低(一般在2-4V),并且其稳定性受栅氧界面陷阱的影响更大。 SiC/SiO2界面的陷阱密度通常高于Si/SiO2界面,这会导致:

Vth漂移: 在高温、高电场应力下,Vth可能发生负漂或正漂(取决于偏置历史和温度)。

Vth对dV/dt更敏感: 较低的Vth本身就是一个弱点。更重要的是,SiC MOSFET为了实现低导通电阻(Rds(on)),其元胞密度通常很高,导致栅漏电容(Cgd,米勒电容)与栅源电容(Cgs)的比值(Cgd/Cgs)通常比硅IGBT或硅MOSFET更大。这意味着在关断过程中,漏极电压快速上升(dV/dt)时,通过Cgd耦合到栅极的电荷量更大(Qg = Cgd * dV/dt)。这个耦合电流会流过驱动回路的阻抗(主要是驱动电阻和栅极回路电感),在栅极上产生一个电压尖峰或抬升。由于Vth本身很低(2-4V),即使一个较小的耦合电压(例如3-5V)叠加在0V的关断电平上,就很可能超过漂移后的Vth,导致器件意外开通(误导通)!这是SiC MOSFET需要负压关断的最主要原因。

2. 开关速度与 dV/dt:

SiC MOSFET: 其最大的优势之一就是极高的开关速度。这得益于碳化硅材料的高临界击穿场强(允许更薄的漂移层)和较高的载流子饱和速度。高速开关意味着极高的dV/dt(可达50-100 V/ns或更高)。正如上面所述,极高的dV/dt通过较大的Cgd耦合到栅极,会产生巨大的位移电流(Idisp = Cgd * dV/dt),显著加剧了误导通的风险。

IGBT: 关断过程存在拖尾电流,导致其关断速度相对较慢(dV/dt通常在5-20 V/μs量级,比SiC MOSFET低几个数量级)。较低的dV/dt意味着通过Cgd耦合到栅极的位移电流小得多,在0V关断时不足以抬升栅压到Vth以上。

3. 寄生参数的影响:

源极电感(Ls): 驱动回路(尤其是功率回路中的源极引线)不可避免地存在寄生电感(Ls)。在高速关断时,急剧变化的漏极电流(di/dt)流经Ls,会产生一个感应电压(Vls = Ls * di/dt)。这个电压是以源极引脚为参考点,加在源极和真实地(芯片源极金属)之间。对于关断状态的器件,驱动芯片输出0V(参考其GND引脚),但由于Ls上的压降,芯片内部实际的栅源电压(Vgs_int) = 驱动电压(0V) - Vls。极高的di/dt(SiC MOSFET的典型特性)会产生一个正的Vls(极性是源极引脚电位高于芯片源极电位),这会导致Vgs_int 瞬时变为负值!这个负压有助于抑制误导通。

IGBT: 较慢的di/dt产生的Vls较小,影响相对不显著。对于SiC MOSFET,虽然Ls产生的负压有一定帮助,但其幅度和持续时间不足以可靠地防止高速、高dV/dt下Cgd耦合导致的误导通,尤其是在多管并联或模块应用中Ls可能不一致的情况下。负压关断提供了一个确定的、更大的负向偏置裕量。

4. 器件结构与电容特性:

SiC MOSFET: 如前所述,为了追求极低的Rds(on),采用高元胞密度设计,这不可避免地增大了单位面积的Cgd。同时,其快速的开关速度放大了Cgd耦合效应。

IGBT: 其结构中存在P+集电极和N-漂移区形成的JFET区和电导调制效应,其电容特性(尤其是Cgd)与SiC MOSFET不同,且dV/dt较低,耦合效应弱。

总结:为什么SiC MOSFET通常需要负压关断?

1. 低且不稳定的阈值电压(Vth): 易受栅氧界面陷阱和温度影响,抗干扰能力弱。

高Cgd/Cgs比值: 米勒电容耦合效应强。

2. 极高的开关速度(高dV/dt,高di/dt): 导致通过Cgd的位移电流(Idisp)非常大,通过Ls产生的感应电压(Vls)变化剧烈。

(1)+(2)+(3)的综合作用: 高dV/dt通过大Cgd耦合产生的大Idisp,在驱动回路阻抗上形成的电压抬升,叠加在0V关断电平上,极易超过较低的、可能已发生漂移的Vth,导致危险的误导通。Ls产生的负压不足以可靠抑制此风险。

3. 负压关断的作用:

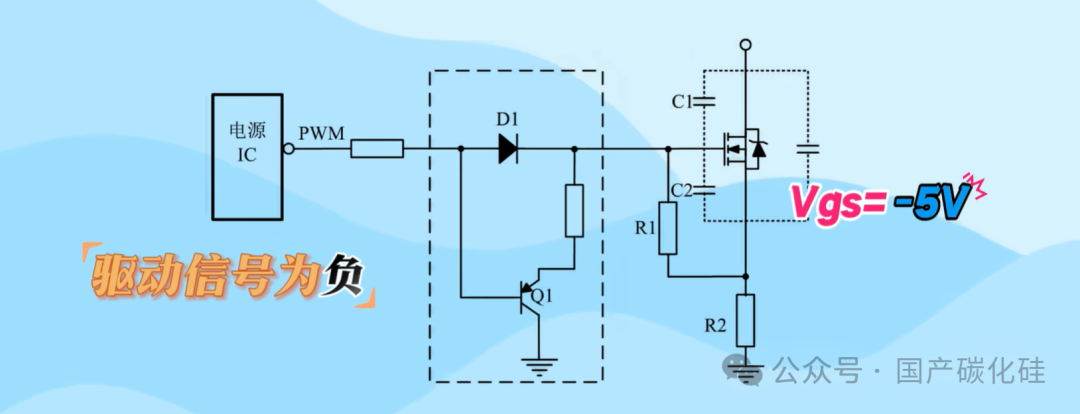

提供一个确定的负偏置(如-2V到-5V),显著增大栅极电压到Vth的“距离”(裕量)。

这个负压裕量能够吸收由Cgd耦合和Ls效应产生的正电压扰动,确保在最坏情况下(高dV/dt,高di/dt,高温,Vth负漂)Vgs_int 始终低于器件的实际阈值电压,从而可靠防止误导通。

提高系统鲁棒性和可靠性,尤其是在桥式拓扑(半桥、全桥)中,下管的关断时刻正好是上管开通产生高dV/dt的时刻,风险最高。

IGBT为什么通常不需要负压关断?

1. 较高且较稳定的阈值电压(Vth): 通常5-7V,抗干扰能力强。

2. 较低的开关速度(低dV/dt): 通过Cgd耦合的位移电流小。

3. 关断米勒平台电压较高(10-15V): 远高于Vth,即使在0V关断,耦合电压也不足以达到Vth。

4. 较低且较慢的di/dt: 源极寄生电感Ls的影响较小。

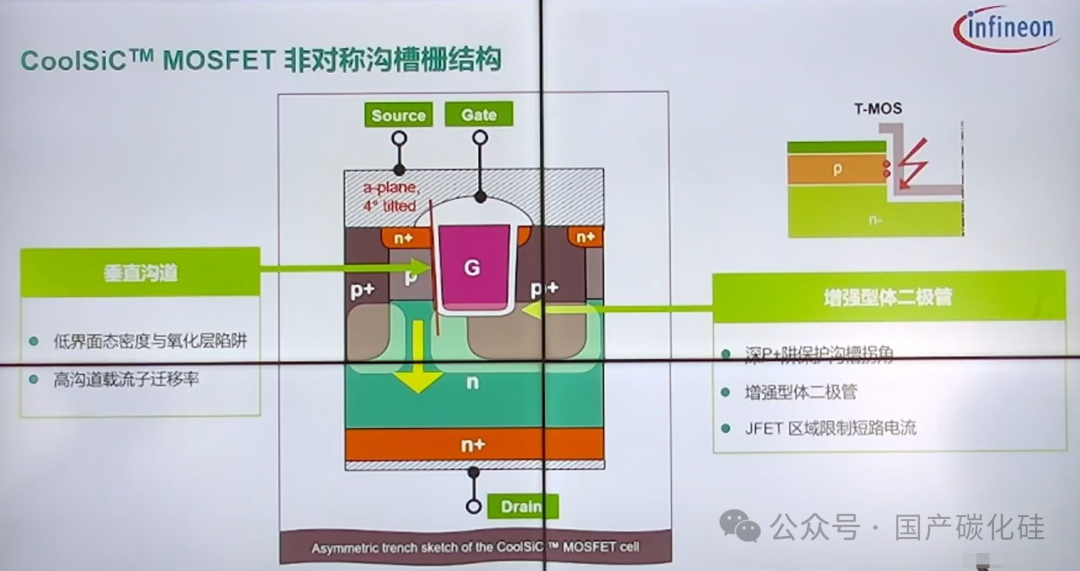

为什么英飞凌部分不需要负压关断?(非对称沟槽结构)

1. 非对称沟槽栅结构(核心创新)

英飞凌CoolSiC MOSFET采用非对称沟槽栅设计,在沟槽的一侧集成深P+阱(Deep P-well),包围沟槽倒角区域。这种结构能显著缓解栅极拐角处的电场集中问题,降低栅氧层承受的电场应力,从而减少界面陷阱密度。

深P+阱设计还抑制了漏极-栅极电容(Cgd)的耦合效应,降低高dV/dt条件下米勒电流对栅极的干扰,从源头上减少误导通风险。

2. 栅氧界面质量优化(阈值稳定性提升)

SiC/SiO₂界面的缺陷是阈值电压(Vth)漂移的主因。英飞凌通过改进栅氧工艺(如M1H技术),大幅降低界面陷阱密度,使Vth在高温、高电场应力下保持稳定(如支持-10V负压操作范围)。

稳定的Vth(典型值2-4V)意味着即使关断时栅压为0V,由dV/dt耦合产生的栅极电压尖峰也难以超过Vth,避免意外导通。

3. 低Cgd/Cgs电容比设计

常规SiC MOSFET为追求低导通电阻(Rds(on))而采用高元胞密度,导致米勒电容Cgd与Cgs比值较高,易受dV/dt耦合影响。英飞凌通过结构优化控制Cgd/Cgs比例,降低栅极串扰敏感性。

尽管非必需,负压关断在特定场景仍能提升英飞凌器件的表现:

1. 降低关断损耗(Eoff):

负压(如-3V)可加速栅极电荷释放,缩短关断时间,减少开关损耗(Eoff),尤其在高频应用中效果显著。2. 增强高温可靠性:

高温下Vth可能略有下降,负压提供额外安全裕量,适用于极端工况(如车载主驱)。3. 抑制寄生振荡:

源极寄生电感(Ls)在关断时产生的负压尖峰(Vls = Ls×di/dt)可能耦合至栅极。负压驱动可抵消此类振荡,提升鲁棒性。

结论

从器件物理本质看,SiC MOSFET需要负压关断的核心驱动力是其高开关速度(高dV/dt)与为实现低导通电阻而必然导致的高Cgd/Cgs比,叠加其固有的低阈值电压和阈值电压不稳定性,共同造成的严重误导通风险。负压关断是解决这一风险最常用、最有效且相对成本较低的手段。而硅IGBT由于其工作原理、结构特点和相对较慢的开关速度,在0V关断时具有天然的、足够的抗误导通能力,因此通常不需要施加负压关断。作为功率工程师,理解这些底层差异对于优化驱动设计、充分发挥SiC性能优势并确保系统可靠性至关重要。

SiC MOS

更多信息请关注

微信公众号

邮箱:ymq@mgmsemi.com

深圳:深圳市光明区光明街道华强科技生态园5A栋1216

成都:成都市高新区双柏路68号汇创天下科技园西区1栋9层907

长沙:长沙市岳麓区麓谷科技创新创业园A1栋2404

上海:上海市闵行区万源路2161弄150号1号楼318

菲律宾:12 Ibayo St, Manila, Metro Manila, Philippines