明古微半导体

MGME SEMICONDUCTOR

碳化硅功率器件+电驱方案

新能源汽车.充电桩.工业电源.光伏储能.电力电子.低空飞行器...

国产碳化硅 就找明古微

技术学院

STUDY

当一颗指甲盖大小的芯片承载着百亿级晶体管高速运转时,很少有人会想到,这背后是半导体工艺历经百年的 “微观雕刻” 革命。从 1947 年贝尔实验室的第一只晶体管,到 2025 年台积电 2nm 工艺的试产,每一次工艺突破都重新定义了电子设备的性能边界。本文将系统拆解半导体工艺的技术内核、演进脉络、产业格局与未来方向,揭开芯片制造的神秘面纱。

半导体工艺技术全景:从基础器件到集成系统

半导体工艺的本质是通过精确控制材料微观结构实现电子功能,按器件类型与集成方式可分为基础单器件工艺、混合集成工艺、特色专项工艺三大类,每类工艺都对应着特定的性能需求与应用场景。

1 基础单器件工艺:电子功能的 “原始积木”

基础工艺以单一晶体管结构为核心,是半导体技术的起点,奠定了后续集成技术的基础。

1. 双极型工艺(Bipolar):模拟放大的 “性能标杆”

核心原理

基于 PN 结的电流控制机制,电子和空穴两种载流子共同参与导电(“双极” 得名于此)。通过发射极向基区注入载流子,基区电流精准调控集电极与发射极之间的主电流,实现信号放大。 关键特点

优势在于跨导高(电流放大能力强)、响应速度快(工作频率可达 GHz 级)、线性度优异,低噪声特性突出,抗辐射能力强,适配高辐射环境如航天设备;短板是集成度低(器件占用面积大)、静态功耗高(导通时持续耗电),难以实现大规模数字集成。 适配芯片

高频低噪声放大器(如射频通信中的信号接收前端,国芯佳品 FC1405 晶体管采用平面 NPN 硅外延双极工艺,专门用于 VHF、UHF 频段放大)、高精度运算放大器(工业控制中的信号处理模块,依赖其线性放大特性)、特种航天器件(卫星载荷中的信号处理器,利用其抗辐射优势)。 代表厂商

安森美(ON Semiconductor)、瑞萨电子,在特种模拟领域仍保持技术优势。

2. 金属氧化物半导体工艺(MOS):数字时代的 “开关基石”

MOS 工艺以场效应晶体管为核心,按沟道类型分为 NMOS、PMOS 及互补结构的 CMOS,其中 CMOS 成为数字电路的绝对主角。

核心原理

通过栅极电压控制沟道内载流子的形成与消失实现开关功能。CMOS 采用互补结构,P 沟道与 N 沟道 MOS 管交替导通,仅在状态切换时产生瞬时电流,静态功耗趋近于零。器件结构从平面 MOS 演进至 FinFET(鳍式)、GAA(全环绕栅极),通过三维结构增强栅极对沟道的控制能力。 关键特点

优势是静态功耗极低(纳安级)、集成度高(3nm 工艺每平方毫米超 1 亿晶体管)、工艺兼容性强,完美契合摩尔定律的微缩需求;短板是驱动能力弱于 Bipolar,高压场景下可靠性不足,模拟性能相对有限。 适配芯片

数字逻辑芯片(CPU 英特尔酷睿 Ultra、GPU 英伟达 Blackwell、手机 SoC 高通骁龙 8 Gen4,均基于先进 CMOS 工艺,台积电 4nm 工艺已成为高端 SoC 主流选择)、低功耗物联网芯片(基于 90nm、55nm 成熟 CMOS 工艺,平衡成本与续航需求)、存储芯片接口电路(DRAM、NAND 闪存的控制单元均采用 CMOS 衍生工艺)。 代表厂商

台积电(先进制程龙头)、三星(GAA 架构先行者)、中芯国际(成熟制程主力)。

3. 功率 MOS 工艺:高压大电流的 “控制核心”

核心原理

通过优化漂移区掺杂浓度与厚度,平衡耐压性能与导通损耗,主要分为横向(LDMOS)和纵向(VDMOS)结构。LDMOS 适合高频高压场景,VDMOS 则侧重高功率密度应用。 关键特点

击穿电压覆盖几十伏至数千伏,开关损耗低,可实现高效能量转换,但高压与低阻特性存在固有矛盾。 适配芯片

射频功率放大器(3G/4G 基站 PA 多采用 LDMOS 工艺,利用其高频特性实现信号远距离传输)、家电功率控制器(空调、冰箱中的逆变器,通过 VDMOS 实现负载调节)。 代表厂商

英飞凌(CoolMOS 系列)、意法半导体,在功率器件领域技术领先。

2 混合集成工艺:多功能融合的 “系统级突破”

混合工艺通过在同一晶圆上集成不同类型器件,实现 “信号处理 - 逻辑控制 - 功率输出” 的一体化,解决了单器件工艺的功能局限。

1. BiCMOS 工艺:模拟与数字的 “性能平衡术”

核心原理

在 CMOS 工艺基础上兼容 Bipolar 器件,形成 “CMOS 逻辑单元 + Bipolar 模拟单元” 的混合结构,通过隔离技术解决不同器件的干扰问题。 关键特点

兼具 CMOS 的低功耗、高集成优势与 Bipolar 的高频、低噪声特性,完美适配数模混合场景。 适配芯片

射频收发器(手机通信模块中的信号处理单元,如高通骁龙 X75 基带芯片的射频前端)、高精度数据转换器(工业测量中的 ADC/DAC 芯片,实现模拟信号与数字信号的精准转换)。 代表厂商

ADI(亚德诺半导体)、德州仪器(TI),在高精度混合信号领域技术壁垒深厚。

2. BCD 工艺:“模拟 + 逻辑 + 功率” 的集成王者

核心原理

1986 年由意法半导体率先研发,通过双阱、三阱甚至四阱工艺,在同一芯片上实现 Bipolar(高精度模拟)、CMOS(逻辑控制)、DMOS(高压功率)三类器件的隔离集成。采用 DTI(深沟槽隔离)、SOI(绝缘体上硅)等技术提升器件兼容性与耐压性能。 关键特点

电压覆盖 1V-1200V,可实现 “信号采集 - 逻辑运算 - 功率驱动” 全链条功能,系统集成度高,减少了芯片间互联损耗。 适配芯片

电源管理芯片(PMIC)(手机快充芯片如 OPPO 120W 快充芯片、笔记本电源适配器)、车载电子控制单元(新能源汽车的车载充电机 OBC、电机驱动模块,意法半导体的 90nm BCD 工艺已广泛用于车载系统)、工业变频器(通过高压 BCD 工艺实现电机转速精准控制)。 代表厂商

意法半导体(BCD 工艺发明者,第 9 代工艺支持 100V 耐压,采用 SOI 技术提升性能)、德州仪器(110nm 工艺支撑 85V 耐压,聚焦汽车电子领域)、华虹半导体(国内 BCD 工艺龙头,90nm 工艺支持 100V-800V 高压,服务新能源汽车与工业客户)。

3 特色专项工艺:场景定制的 “技术护城河”

特色工艺跳出单纯的尺寸微缩,通过材料创新或结构优化满足特定场景需求,成为差异化竞争的关键。

1. 射频工艺:无线通信的 “信号桥梁”

核心原理

按材料分为三类 ——RF CMOS(硅基,低成本)、GaAs(砷化镓,高频低噪)、GaN(氮化镓,高压高效),分别适配不同频率与功率需求。 关键特点

RF CMOS 成本低、集成度高,适合中低频消费电子;GaAs 在 10GHz 以上频率性能突出,噪声系数低,但 ESD 等级低易损坏;GaN 开关频率高、功率密度大,耐受电压可达千伏级。 适配芯片

手机射频前端(Skyworks 的 GaAs PA 用于 iPhone 通信模块)、5G 基站功率放大器(华为 5G 基站采用 GaN PA,实现宽频带信号覆盖)、卫星通信器件(GaAs 工艺用于星载接收机,抗干扰能力强)。 代表厂商

Skyworks、Qorvo(GaAs 器件龙头,垄断高端射频市场)、稳懋(全球最大 GaAs 代工厂,服务 Broadcom、高通等客户)、三安光电(国内 GaN 工艺领先者,支撑消费电子快充与基站应用)。

2. 存储专项工艺:数据时代的 “记忆基石”

存储工艺聚焦电荷存储与读取机制,按读写特性分为易失性与非易失性两类,核心挑战是密度提升与可靠性保障。

DRAM 工艺

通过电容存储电荷,需高频刷新(约 64ms 一次),技术从平面转向堆叠,当前最先进为 1β 节点(10nm 级),采用 HKMG(高 K 金属栅)技术降低漏电。适配电脑内存(DDR5)、手机运行内存(LPDDR5X),代表厂商为三星、SK 海力士、美光。 NAND Flash 工艺

从 2D 平面演进至 3D 堆叠,三星已实现 512 层 V-NAND 量产,通过 Xtacking 架构提升读写速度。适配固态硬盘(SSD)、手机存储(UFS 4.0),长江存储 232 层 3D NAND 已实现量产。 关键制造难点

3D NAND 的台阶刻蚀需实现 70:1 的高深宽比,每片晶圆含一万亿个平行通孔,对刻蚀精度要求极高。

3. MEMS 工艺:“微观机械 + 电子” 的融合创新

核心原理

融合半导体制造与精密机械加工,通过光刻、刻蚀形成微米级机械结构(如悬臂梁、谐振器),实现 “感知 - 执行” 一体化。 关键特点

体积小、精度高,可与 CMOS 电路集成,实现智能化感知。 适配芯片

消费电子传感器(手机陀螺仪如苹果 iPhone 的运动感知模块、气压传感器)、汽车传感器(胎压监测传感器、发动机振动传感器)、医疗器件(微流控芯片用于血液检测,精度达纳升级)。 代表厂商

博世(汽车 MEMS 龙头)、意法半导体、歌尔股份(国内消费电子 MEMS 主力)。

4. 第三代半导体工艺:宽禁带材料的 “性能飞跃”

以 SiC(碳化硅)、GaN 为核心,突破硅基材料的物理极限,适配高温、高压、高频场景。

SiC 工艺

需在导电衬底上生长外延层制造器件,击穿场强是硅的 10 倍,耐高温特性突出。适配新能源汽车逆变器(特斯拉 Model 3 采用 SiC MOSFET)、光伏逆变器,可降低电池能耗 10%。代表厂商:WolfSpeed(美国)、意法半导体、英飞凌等。 GaN 工艺

开关频率是硅基的 10 倍以上,可缩小器件尺寸 30% 以上。适配消费电子快充(小米 65W 氮化镓充电器)、5G 毫米波 PA,2026 年电信领域市场规模预计超 2 亿美元。代表厂商:Navitas、英飞凌、纳微半导体。

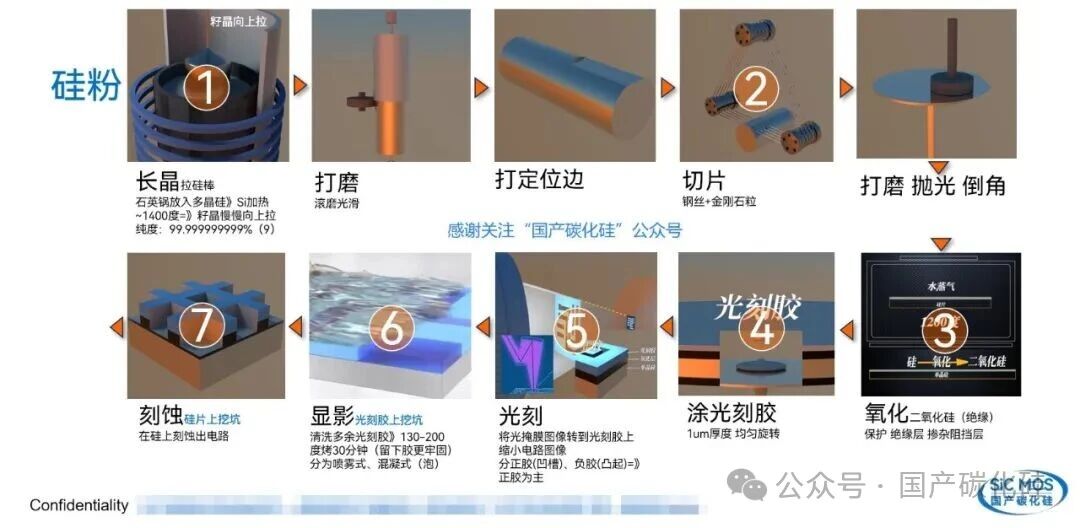

4 制造核心支撑工艺:精准控制的 “关键工序”

如果说器件工艺是 “设计蓝图”,制造支撑工艺就是 “施工工具”,决定了蓝图能否精准落地。

1. 光刻工艺:电路图案的 “精准投影”

核心原理

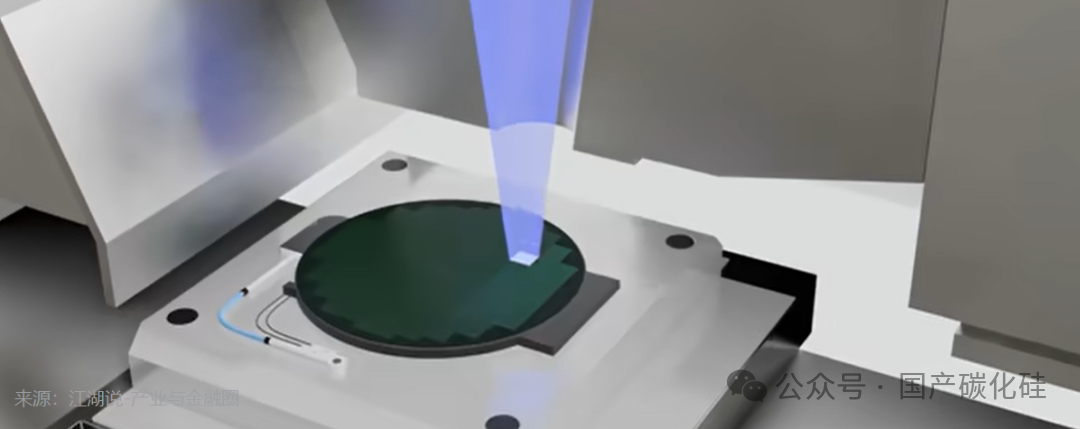

将掩膜版上的电路图案通过光源投影到硅片表面的光刻胶上,经曝光、显影形成临时图案,是决定制程精度的核心环节。 技术演进

从汞灯(微米级)→深紫外(DUV,193nm,支持至 7nm)→极紫外(EUV,13.5nm,5nm 及以下),光源波长持续缩短,精度不断提升。 关键特点

EUV 可实现原子级精度,但设备成本超 1.5 亿美元,全球仅 ASML 能量产。 代表厂商

ASML(EUV 垄断者)、佳能、尼康(DUV 设备)。

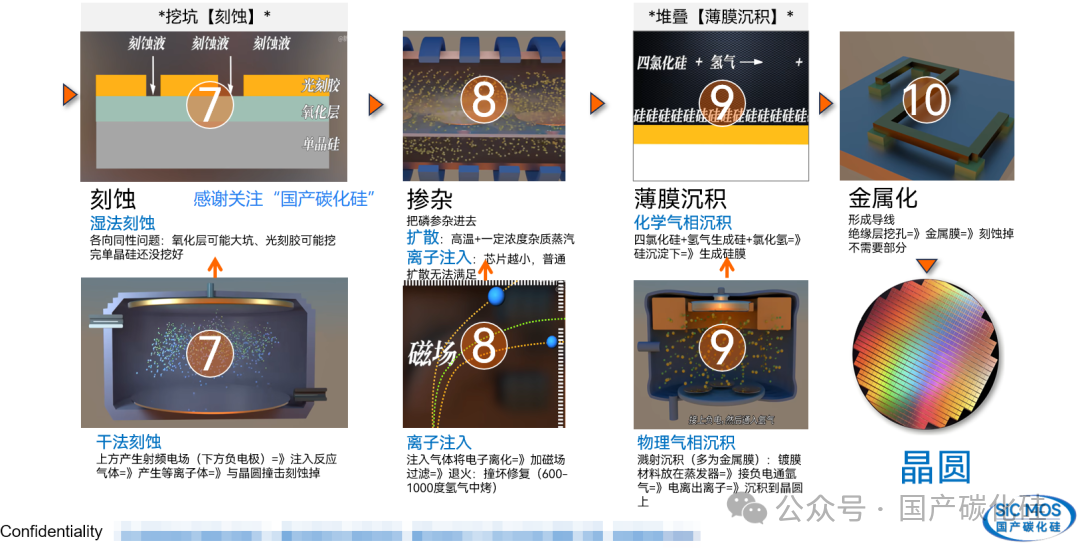

2. 刻蚀工艺:微观结构的 “精细雕刻”

核心原理

作为芯片制造的 “关键减法”,通过化学或物理方法选择性去除未被光刻胶保护的材料,形成沟槽、通孔等微观结构,类比 “用模板雕琢蛋糕花纹”。 技术分类

湿法刻蚀(用氢氟酸等化学溶液溶解材料,成本低但精度差,用于 28nm 以上成熟制程或清洗环节);干法刻蚀(以等离子体为 “刻蚀剂”,通过离子轰击 + 化学反应实现去除,精度可达 1nm 以内,占比超 90%,又分为 CCP(电容性,适用于硬介电材料)和 ICP(电感性,适用于硅、金属)两类)。 关键挑战

3D NAND 刻蚀需实现 70:1 的高深宽比,一万亿个通孔需保持平行规整,难度与模具高度平方成正比。 代表厂商

应用材料、泛林半导体、东京电子(全球市占超 90%)、中微公司(国内龙头,覆盖 95% 刻蚀需求)。

3. 掺杂工艺:电学特性的 “精准调控”

核心原理

向半导体材料中引入杂质原子改变电学性质,从传统热扩散演进至离子注入技术,可精确控制掺杂浓度与深度。 关键技术

等离子体浸没离子注入(PIII)减少晶格损伤,提升掺杂均匀性,适配先进制程需求。 代表厂商

应用材料(离子注入机龙头)、北方华创(国内设备突破)。

半导体工艺百年演进史:从实验室到产业革命

半导体工艺的发展是人类对微观世界控制能力不断突破的历史,大致可分为六个关键阶段,每阶段都以核心技术突破为标志。

1. 萌芽期(1940s-1950s):晶体管的诞生

1947 年:贝尔实验室发明点接触晶体管,替代真空管开启半导体时代。 1954 年:硅晶体管问世,解决了锗晶体管耐高温性差的问题。 1958 年:德州仪器发明第一块集成电路,采用 Bipolar 工艺,集成 2 个晶体管,开创器件集成新纪元。 技术特征

以锗、硅材料为主,工艺精度毫米级,主要用于军事雷达、早期计算机。

2. 成长期(1960s-1970s):CMOS 的崛起

1963 年:仙童半导体提出 CMOS 工艺原理,解决了 Bipolar 的功耗问题,但受限于光刻技术未能立即产业化。 1971 年:英特尔推出 4004 处理器,采用 10μm Bipolar 工艺,集成 2300 个晶体管。 1975 年:摩尔定律正式提出,预测晶体管密度每 18-24 个月翻倍。 技术特征

硅材料成为主流,工艺节点降至微米级(10μm-1μm),开始探索器件集成规律。

3. 成熟期(1980s-1990s):工艺分化与集成突破

1980s:CMOS 工艺实现规模化应用,逐步取代 Bipolar 成为数字电路主流;DMOS 工艺突破,推动功率半导体产业化。 1986 年:意法半导体研制成功 BCD 工艺,解决模拟、数字、功率器件集成难题。 1993 年:英特尔奔腾处理器采用 0.8μm 工艺,开启 PC 普及浪潮。 1998 年:铜互联技术替代铝互联,降低线延迟,支撑 180nm 制程量产。 技术特征

工艺节点从 1μm 降至 0.18μm,光刻、刻蚀等关键工序走向成熟,HKMG 技术开始研发。

4. 黄金期(2000s-2010s):摩尔定律的巅峰

2004 年:台积电量产 90nm 工艺,引入低 K 介质材料,降低互联延迟。 2011 年:英特尔量产 22nm FinFET 工艺,晶体管从平面走向三维,突破物理极限。 2015 年:三星与台积电相继量产 14nm 工艺,FinFET 技术成熟,支撑智能手机 SoC 性能爆发。 2018 年:台积电 7nm 工艺量产,首次引入 EUV 光刻,华为麒麟 980 成为首款 7nm 手机芯片。 技术特征

工艺节点从 90nm 快速微缩至 7nm,集成度每代提升约 1 倍,先进封装技术(CoWoS)开始兴起。

5. 转型期(2020s 至今):多元技术路线并行

2022 年:台积电与三星量产 3nm 工艺,后者采用 GAA 架构,进一步提升栅极控制能力。 2023 年:长江存储量产 232 层 3D NAND,存储密度达 1.3Tb / 平方毫米;中芯国际 14nm 工艺良率稳定在 80% 左右。 2024 年:WolfSpeed 8 英寸 SiC 晶圆厂满产,推动车规 SiC 器件成本下降;台积电 CoWoS 封装产能翻倍,支撑 AI 芯片需求。 2025 年:台积电宝山 F20 工厂启动 2nm 试产,ASML High-NA EUV 光刻机交付,全球先进制程产能达 220 万片 / 月。 技术特征

先进工艺逼近物理极限,成熟工艺(28nm、40nm)因汽车、物联网需求焕发活力,第三代半导体加速商业化。

全球厂商竞争格局:技术壁垒与市场分化

半导体工艺领域形成了 IDM(垂直整合制造)与 Foundry(晶圆代工)并存的产业模式,不同厂商基于技术积累与市场定位形成差异化竞争力,呈现 “头部垄断、中腰部差异化、本土厂商追赶” 的格局。

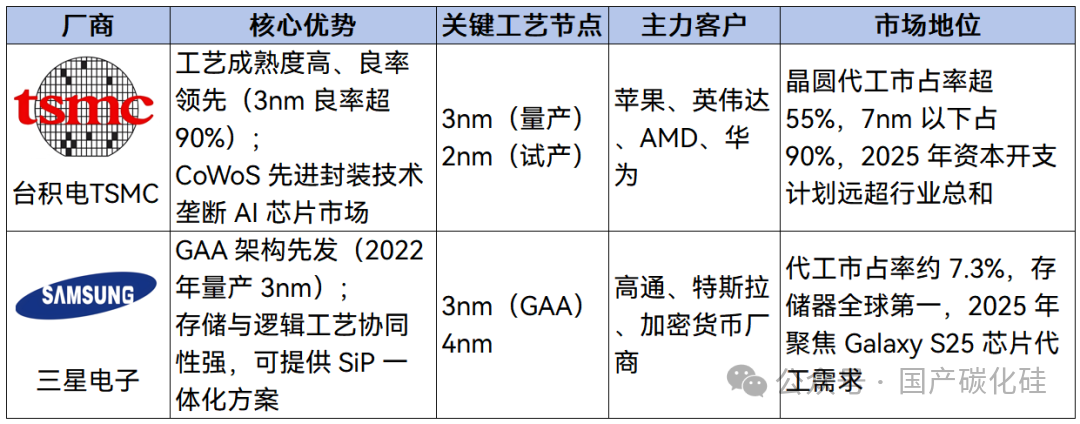

1 先进制程领导者:台积电与三星的双雄争霸

2 成熟与特色工艺巨头:技术深耕与场景绑定

1. 德州仪器(TI):模拟芯片的 “隐形王者”

核心优势

专注 65nm 以上成熟制程,自控 300mm 晶圆产能,BCD 工艺与功率器件技术领先,车规芯片寿命达 15 年。 市场表现

2023 年模拟芯片市占率约 19%,毛利率超 65%,汽车与工业市场贡献 70% 营收,其 110nm BCD 工艺支撑 85V 耐压需求。

2. 意法半导体(ST):BCD 与功率器件先锋

核心优势

BCD 工艺发明者,第 9 代工艺采用 SOI 技术支持 100V 耐压;通过收购 Norstel 强化 SiC 布局,8 英寸晶圆已量产。 市场绑定

车载 PMIC 市占率全球第一,SiC MOSFET 供应特斯拉,与博世、大陆集团深度合作。

3. 英飞凌(Infineon):功率半导体龙头

核心优势

DMOS 与 IGBT 工艺技术领先,CoolMOS 超结系列导通电阻比传统 MOS 低 50%;GaN/SiC 工艺布局完善,新能源汽车 IGBT 模块市占率超 25%。 应用聚焦

工业电源、新能源汽车逆变器,是比亚迪、大众的核心供应商。

4. 安森美(ON Semiconductor):车规功率器件专家

核心优势

IGBT 工艺全球第二(市占率 19%),Bipolar 工艺在特种模拟领域领先,抗辐射器件适配航天场景。 市场突破

车规 IGBT 供应比亚迪、大众电动车,2024 年产能利用率重回超负荷状态。

3 中国本土力量:从成熟制程到特色突破

1. 中芯国际(SMIC):本土工艺 “扛旗者”

技术进展

28nm/45nm/55nm 成熟工艺量产,良率超 90%,占全球 28nm 产能约 10%;14nm FinFET 工艺 2019 年量产,用于华为麒麟 710A 芯片;7nm 工艺通过 DUV 多重曝光研发,预计 2025 年试产。 特色布局

180nm BCD 工艺用于电源管理芯片,55nm RF CMOS 支持 4G 通信,车规工艺通过 AEC-Q100 认证。 市场地位

全球代工市占率约 5.9%,受益国产替代需求,2024 年产能利用率实现 “V 型” 反弹。

2. 华虹半导体:特色工艺 “隐形冠军”

核心优势

90nm BCD 工艺国内领先,支持 100V-800V 高压,全球 BCD 市占率约 5%;65nm IGBT 工艺导通损耗低 20%,进入比亚迪供应链;55nm eFlash 工艺替代英飞凌部分车规 MCU 订单。 市场表现

2024 年 Q4 产能利用率重回超负荷,汽车电子与工业控制需求驱动增长。

3. 长江存储(YMTC):存储工艺突破者

技术突破

2023 年推出 232 层 3D NAND,采用 Xtacking 架构,读写速度比传统方案快 30%,存储密度达 1.3Tb / 平方毫米。 市场进展

全球 NAND 市占率约 5%,进入国内 SSD 厂商供应链,目标 2030 年突破 20%。

4. 设备与材料支撑厂商

中微公司:刻蚀设备覆盖 95% 应用需求,TSV 刻蚀设备国内市占率领先,2023 年收入近 60 亿元。 北方华创:实现刻蚀、薄膜沉积等设备全覆盖,支撑成熟制程产能建设。 三安光电:6 英寸 SiC 衬底量产,GaN 工艺用于消费电子快充,进入特斯拉供应链。

4 设备材料垄断者:上游的 “卡脖子” 力量

光刻机

ASML 垄断 EUV 市场,High-NA EUV 预计 2025 年交付,单台成本超 3 亿美元。 刻蚀机

应用材料、泛林半导体、东京电子占据超 90% 份额,技术壁垒极高。 特种材料

日本信越、SUMCO 供应全球 70% 以上的硅片;美国陶氏化学的光刻胶支撑先进制程需求。

未来发展方向:突破物理极限的多维创新

随着硅基工艺逼近原子级极限(3nm 以下量子隧穿效应显现),半导体工艺已从单一 “尺寸竞赛” 转向 “材料创新 + 架构革新 + 集成模式” 的多元突破,未来将呈现三大发展主线。

1 先进逻辑工艺:从三维结构到原子级控制

器件架构革新

3nm 以下全面采用 GAA 架构,台积电 2nm 工艺将引入叉片晶体管(Forksheet),集成度较 3nm 提升 20%;后续互补场效应晶体管(CFET)通过垂直堆叠进一步提升密度。 新材料应用

采用二维材料(MoS₂)替代硅沟道,解决量子隧穿问题;引入钴 / 铜合金互联材料,降低线延迟;高 K 介质材料持续升级,提升栅极控制能力。 光刻技术突破

ASML High-NA EUV 光刻机将最小线宽降至 5nm 以下,结合多重曝光技术(SAQP、SADP)实现 2nm 及以下制程,单台设备成本超 3 亿美元,进一步抬高行业门槛。

2 特色与成熟工艺:场景定制与性能升级

BCD 工艺三向分化

高压方向(500-700V)采用 RESURF 技术提升耐压,瞄准工业功率控制;高功率方向(40-90V)强化车规鲁棒性;高密度方向(5-50V)集成 MCU 与存储器,服务智能驱动场景。 第三代半导体量产提速

SiC 基器件在新能源汽车逆变器渗透率将从 2025 年的 30% 升至 2030 年的 60%,成本较硅基下降 40%;GaN 在 5G 毫米波 PA、激光雷达驱动领域快速渗透,2026 年市场规模突破 50 亿美元。 成熟制程绿色化

通过低功耗光刻胶、晶圆回收技术降低能耗,台积电 3nm 工艺较 5nm 功耗降低 35%;晶圆厂加速采用绿电,三星德州工厂计划 2030 年实现 100% 绿电供电。

3 集成与制造模式革新:超越摩尔定律的核心路径

Chiplet 异构集成

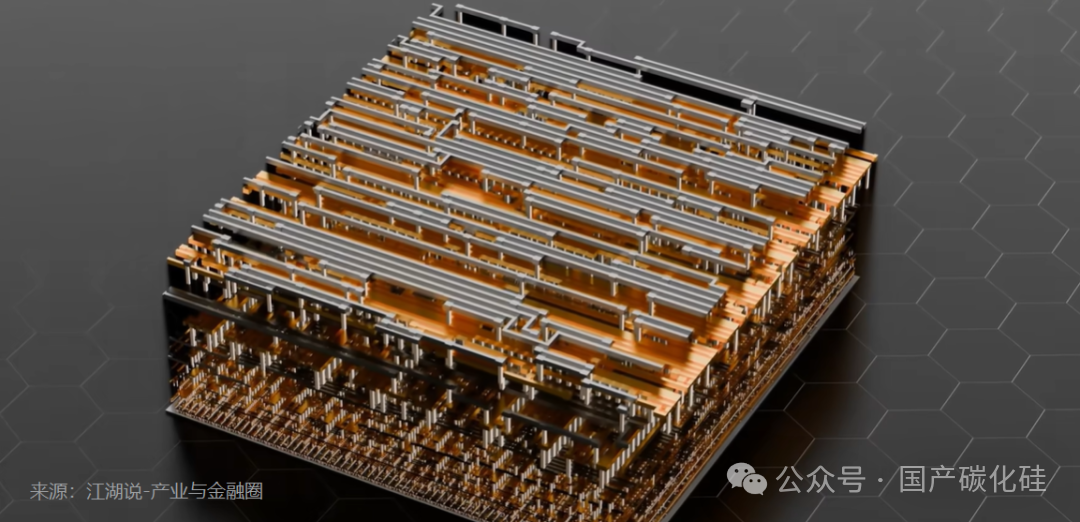

将 CPU、GPU、HBM 等不同工艺裸片通过先进封装集成,突破单芯片物理限制。台积电 CoWoS、英特尔 Foveros 技术已规模化应用,英伟达 H200 采用 Chiplet 设计,算力较 H100 提升 2 倍。 3D 晶圆堆叠

通过 TSV(硅通孔)技术实现垂直互联,SK 海力士已实现 8 层 HBM3E 堆叠,未来层数将突破 12 层,数据传输带宽提升至 1TB/s 以上。 制造智能化

引入 AI 全流程监控,中芯国际在 28nm 工艺中采用机器学习优化刻蚀参数,良率提升 5 个百分点;台积电通过数字孪生技术模拟制程偏差,研发周期缩短 30%。

4 产业挑战与地缘博弈

技术瓶颈

EUV 光刻机、高端光刻胶等 “卡脖子” 环节制约先进制程突破,美国对华出口管制加剧技术迭代难度。 成本压力

单代先进工艺研发费用超 100 亿美元,3nm 晶圆成本达 3 万美元,仅头部厂商能承担投入。 产能分化

2025 年全球先进制程产能增长 16%,成熟制程增长 5%,中国大陆成熟制程占比将升至 47%,但高端产能仍集中于中国台湾、韩国。

结语:工艺革命永无止境,场景创新定义未来

从 1947 年的点接触晶体管到 2025 年的 2nm GAA 芯片,半导体工艺用 78 年时间完成了从 “毫米级粗放加工” 到 “原子级精准雕刻” 的蜕变。当硅基工艺逼近物理极限,材料创新(SiC/GaN)、架构革新(Chiplet)与集成模式(BCD)正在开辟新赛道。全球格局中,台积电、三星掌控高端话语权,德州仪器、意法半导体在特色领域建立壁垒,而中国正通过成熟制程夯实基础、特色工艺寻求突破。这场工艺竞赛早已不是单一的 “尺寸比拼”,而是 “性能、成本、可靠性、场景适配” 的多维平衡艺术。

未来 10 年,AI、新能源、空间通信的爆发将催生更多定制化工艺需求。在这场没有终点的 “微观革命” 中,那些能精准把握场景需求、持续突破技术边界的企业,终将成为下一代半导体产业的定义者。

国产碳化硅,就找明古微--感谢深圳市明古微半导体有限公司长期对本公众号的赞助与支持,深圳市明古微半导体有限公司作为爱仕特科技碳化硅MOS/SBD、中科本原DSP、乐山希尔整流桥堆/FRD等的核心代理商,与其深度合作并联合开发功率模块及电驱、储能系统,为电动汽车、OBC、DC-DC、充电桩、光伏逆变、SVG、PCS、工业电源、家电变频等能源产业提供完整解决方案,更多信息请登录:wwwmgmsemi.com

SiC MOS

更多信息请关注

微信公众号

邮箱:ymq@mgmsemi.com

深圳:深圳市光明区光明街道华强科技生态园5A栋1216

成都:成都市高新区双柏路68号汇创天下科技园西区1栋9层907

长沙:长沙市岳麓区麓谷科技创新创业园A1栋2404

上海:上海市闵行区万源路2161弄150号1号楼318

菲律宾:12 Ibayo St, Manila, Metro Manila, Philippines